在并发编程中,程序员往往习惯于按照源代码或编译后汇编上的顺序来推理程序行为。然而即便编译器不重排,CPU 和内存子系统也可能以不同于程序所写顺序使内存访问在全局变得可见,这就是所谓的硬件内存重排序。理解内存重排序对于构建正确、安全且高效的并发程序至关重要,尤其是在实现锁、同步算法或无锁数据结构时。下面从模型、实例、底层原因、屏障指令及实战建议几个维度展开细致解析。 何谓顺序一致性与为何它直观但昂贵 顺序一致性是最直观的内存一致性模型:每个线程的内存访问在系统中以程序顺序变得可见,多个线程的访问在全局上形成某种总序,但任何单个线程内部保持原始的程序顺序。基于顺序一致性的并发推理通常较为简单,因为可以将每个线程视作按顺序执行。

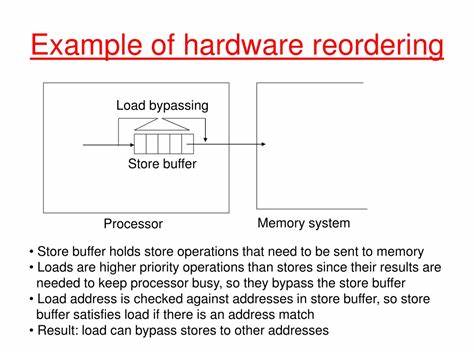

不过,现代处理器如果严格执行顺序一致性,性能会受到严重影响。为提高吞吐量和延迟表现,处理器与内存子系统允许在满足一定约束下重新排序内存操作,从而出现比顺序一致性更弱的模型。 x86 的 Processor Consistency 与常见的重排序模式 x86 架构通常遵循一种被称为 Processor Ordering 或 Processor Consistency 的模型。相较于顺序一致性,x86 最大的放宽点在于允许写操作与随后读操作重排,也就是所谓的 Store->Load 重排序。简单来说,处理器可以将写操作放入存储缓冲区而不是立刻对其他核心可见,然后继续执行后续的读操作。如果这些读操作触发缺失且未与存储缓冲区中项冲突,就可能在全局上先看到读结果,导致程序语义偏离程序顺序的假设。

其余如写写、读读、读写在 x86 上通常被保证不重排,或者仅在特定条件下受限。 用经典 Peterson 算法说明 Store->Load 重排序的威力 Peterson 算法用于两个线程之间的互斥,核心状态包括 interested 数组和 turn 变量。实现思路为:线程先表明有兴趣进入临界区(写 interested[tid]=1),随后设置 turn=other,最后在循环中检查对方是否既感兴趣又被赋予了优先权。理想情况下,只有一个线程能进入临界区。把这个算法直接按自然写法用 C++ 实现后,在 x86 平台上运行大批量实验有时会出现违反互斥的结果,最终计数小于期望值。通过查看生成的汇编并结合硬件模型分析,可以发现问题在于两个线程各自把 writes 缓存在 store buffer 中,而 reads 在 store 被提交到内存前就已观测到旧值,从而两者都误判对方不感兴趣,导致同时进入临界区。

store buffer 与内存可见性:为什么即使是按序执行的 CPU 也会重排序 很多人误以为只有乱序执行(Out-of-Order)CPU 会导致内存重排序,但事实并非如此。处理器通常配备 store buffer 来缓存写操作,写入不必马上写回到缓存层或内存。无论是乱序执行还是顺序执行的核心,在写入进入 store buffer 后,写在局部看起来已完成,但对其他核心尚未可见。随后发出的读指令可以直接从 cache/memory 读到数据,而不必等待 store buffer 中的旧写写回,从而在全局表现为写在读之后,形成 Store->Load 重排序。因此,store buffer 是导致此类重排序的主要硬件来源之一。 内存屏障(fence)如何解决重排序问题 为防止硬件重排序,x86 提供了屏障指令概念化的接口,常见的有 mfence、sfence、lfence。

mfence 保证在它之前的所有 load 与 store 在全局可见性上都完成后,才允许它之后的 load 与 store 执行。sfence 专注于 store 的顺序,lfence 专注于 load 的顺序。对于经典的 Peterson 场景,需要保证在写 interested[tid] 之后,后续对 interested[other] 的读不能被提前观察到。因此在写入 interested 和读取对方兴趣之间插入 mfence 能确保先前的 store 对所有线程可见后再继续执行读,从而恢复程序期望的互斥语义。 软件层面的更好选择:C++11 原子模型与内存语义 尽管可以在汇编或通过平台内建函数显式插入屏障,但多数现代 C++ 项目应优先使用语言提供的原子类型与内存顺序,如 std::atomic 与 memory_order。C++11 定义了多种内存顺序:memory_order_seq_cst、memory_order_acq_rel、memory_order_acquire、memory_order_release、memory_order_relaxed 等。

memory_order_seq_cst 提供最强的全局顺序保证,常对应底层实现的强屏障或合成的同步操作,而 acquire/release 语义为读和写提供了更细粒度且更高效的同步表达。将变量包装为 std::atomic 并用合适的内存序进行读写,通常能避免手动使用平台屏障且具备良好可移植性。 volatile 不是同步工具:常见误区与风险 很多开发者在尝试使变量在多线程间可见时会使用 volatile 关键词,但 volatile 仅仅告诉编译器不要对访问进行某些优化或寄存器缓存,它并不能提供关于内存可见性或排序的跨线程保证。在多线程同步场景下把 shared 状态声明为 volatile 而不是 std::atomic,是容易导致难以察觉的竞态和重排序错误的做法。应把 volatile 视为与并发同步无关的工具,而将内存同步交给原子和屏障来处理。 如何在代码中实际使用 mfence 与平台内建函数 在需要直接控制硬件屏障的极端性能或底层库场景,可以使用 x86 的内建屏障,如 GCC/Clang 下的 __sync_synchronize 或 _mm_mfence(来自 xmmintrin.h)。

__sync_synchronize 在许多平台上生成完整的内存屏障。示例性用法是在写入关键的控制标志后马上调用屏障,然后再读其他位置,从而阻止 Store->Load 重排。需要注意的是,mfence 会带来性能开销,特别是频繁使用会导致吞吐下降;因此应审慎使用,仅在必要的同步点插入。 调试硬件重排序引发的并发错误的方法 调试此类问题通常比普通数据竞争更难,因为错误往往发生间歇且难以复现。几个有效的技术包括:通过增加日志和计数来扩大可观察性;在关键点插入短暂停(sleep / pause 指令)以改变时间窗口;使用 perf 或 objdump 等工具查看生成汇编,确认内存访问顺序;使用线程杀手测试或小型 litmus 测试来验证特定重排序模式;使用动态检测工具如 ThreadSanitizer 来捕获数据竞争,但要明白某些重排序并不总是被 TSAN 报告为传统竞态。此外,通过单核运行、禁用超线程或降低优化级别可以帮助重现问题以便定位。

跨架构差异:ARM 与 POWER 的更弱模型与屏障指令 x86 的一致性模型相对严格,除了 Store->Load 重排外大多数序列被保证。然而 ARM 和 POWER 等架构采用更弱的内存模型,允许更多类型的重排序。它们提供了不同的屏障指令,如 ARM 的 DMB、DSB、ISB,用于不同强度的屏障语义。编写可移植的并发代码时,使用语言级原子与合适的内存序非常重要,因为编译器与标准库会为目标平台生成适当的指令序列以维持语义。 性能权衡与最佳实践 在并发程序中追求正确性优先于微观性能,但在高频率同步操作的场景下,合理的设计可以同时兼顾两者。优先采用语言层面的原子与锁,避免手工插入低级屏障。

尽量使用 acquire/release 语义替代强序列化的 seq_cst,除非确有全局顺序需求。在实现算法时考虑使用无锁容器库或成熟的并发原语,重用已被社区验证的实现。只有当语言层工具无法满足需求时,再考虑使用平台特定屏障,并做好微基准和广泛测试来衡量性能影响。 结论:把握硬件重排序是构建可靠并发系统的关键 硬件内存重排序是并发系统设计中的现实挑战,理解处理器内存模型、store buffer 的作用与屏障指令的语义,能帮助开发者在设计同步算法与调试复杂竞态时做出正确选择。对于大多数应用,优先使用 C++11 的 std::atomic 与合适的内存序是兼顾可读性、可移植性与性能的最佳路径;在底层库或极端优化场景中,可结合平台屏障和详尽测试以保证语义正确。掌握这些技术细节,能显著降低并发错误风险,并在必须时用恰当工具和屏障恢复程序的期望行为。

。