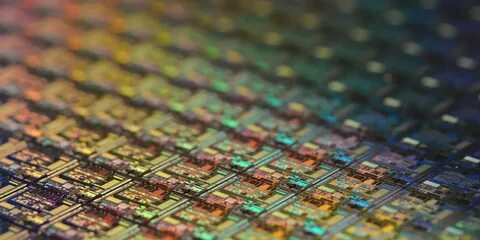

随着科技的不断进步,芯片制造技术也在持续挑战物理极限,进入更小的纳米尺度。作为全球领先的半导体代工厂,台积电(TSMC)近年来不断刷新制程节点的创新纪录。最新消息显示,台积电计划在2028年实现1.4纳米芯片制程技术的量产,这不仅标志着芯片工艺进入一个全新的阶段,也预示着半导体产业链将面临许多新的机遇和挑战。台积电此次公布的1.4纳米芯片制程虽然名称引发了一定的混淆,但核心科技进步的意义无可忽视。芯片制程节点越小,通常意味着晶体管尺寸缩小,能够容纳更多的晶体管数量,从而提升计算能力和能效,为智能手机、人工智能、高性能计算和自动驾驶等领域带来革命性的性能提升。然而,进入1.4纳米门槛对制造过程中的材料科学、量子效应管理及散热技术提出了更高要求。

实际上,芯片命名有时候会成为半导体行业争议的焦点。1.4纳米这一命名尽管引发了一些业内专家的困惑,原因在于现实中物理上的晶体管尺寸与命名节点并不完全对应,更多是一种营销和技术代表符号。这种命名策略有时使外界难以准确理解制程技术的实际性能指标。因此,理解台积电1.4纳米所代表的是工艺性能的提升,而非单纯晶体管物理尺寸,是对这项技术合理看待的关键。展望未来,台积电1.4纳米制程技术将基于极紫外光刻(EUV)和更先进的多重曝光技术,结合创新的晶体管设计,比如GAAFET结构,进一步优化晶体管的开关效率和电流控制能力。这样的创新不仅提升单芯片性能,还显著降低了功耗,对于推动5G、人工智能芯片乃至量子计算硬件的实际应用具有深远意义。

同时,随着芯片制程微缩,制造难度也成倍增加。台积电需要投入巨额资金和多学科跨领域合作来解决纳米级别材料应力、晶体管间电干扰等一系列技术难题。产业链上的供应商和客户也必须适应这些变化,推进新材料研发和工厂设备升级。台积电未来几年的技术路线图不仅把握着自身在全球半导体市场的领先地位,更将影响整个产业生态的发展轨迹。中国大陆、美国及欧洲等全球多地均在积极布局先进芯片制造能力,但台积电凭借积累的技术底蕴和强大的研发实力,仍然是许多国际大厂首选的制造合作伙伴。台积电1.4纳米芯片技术的到来还有望加速芯片设计架构的创新。

设计公司可以依托更先进的制造工艺,实现更复杂的集成电路和更高的计算效率,提升用户终端的应用体验。特别是在人工智能、虚拟现实、自动驾驶等应用场景中,对芯片算力和能效的需求持续攀升,推动产业创新加速。总之,台积电宣布的1.4纳米芯片技术是半导体行业迈向极限微缩的重要标志,虽然命名存在一定争议,但技术的突破不可小觑。这一技术不仅代表着单晶体管功耗和性能的双重优化,还将激发上游材料供应商、设备厂商和下游设计团队的协同创新。预计到2028年,随着量产落地,1.4纳米制程芯片将广泛应用于高端计算、高速通讯及智能终端领域,成为引领新一代数字经济发展的核心引擎。了解和关注台积电这项技术发展动态,对于行业从业者、投资者以及科技爱好者来说,都具有重要参考价值。

未来半导体产业的竞争将更加依赖对先进制程的掌控能力,1.4纳米时代的到来,必将开启芯片技术和应用的新时代。