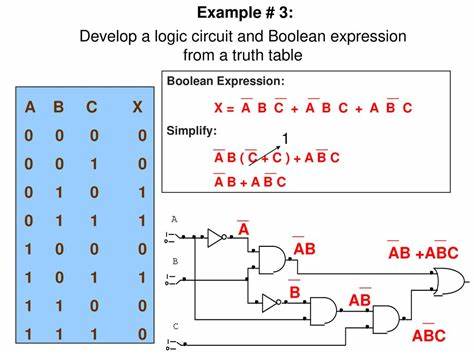

布尔电路作为数字电路设计的基础,近年来在计算机科学与电子工程领域引发了广泛关注。尤其是4输入2输出布尔函数的最优实现问题,因其复杂度和应用价值成为研究热点。2020年,一项耗费数千CPU核心小时的深入研究,成功揭示了4输入2输出布尔电路最小实现电路的完整结构与分类,为布尔逻辑优化领域开辟了新路径。布尔函数数量巨大,4输入2输出共有2的32次方种不同的函数,而其搜索和优化的复杂度远超以往更简单的配置。研究通过对函数应用等价关系的群论分析,有效缩小了搜索空间,将所有布尔函数划分为约147万多种等价类。该等价类划分基于输入和输出变量的置换、取反操作,这种方法极大地帮助研究者减轻了冗余计算,提高了算法效率。

研究采用广度优先搜索算法,在近3750核心小时的强大计算资源支持下,详细探测了电路从简单到复杂的结构演化过程,明确了各类布尔函数在电路门数消耗上的最优解。该算法巧妙利用了输入对称性和布尔函数之间的关系,将深度达到8级的巨大搜索树完整构建,节点数量达170多亿,展示了布尔电路复杂度的真实景象。搜索中,每个节点代表特定布尔函数集的最优实现阶段,随着深度递增,电路成本逐渐增长,反映出实现复杂功能的门数需求。分别代表不同成本类别的函数样例如恒0函数、输入直接输出、两输入的AND和XOR组合,直观表达了电路成本与功能复杂度的对应关系。研究中值得注意的是,有19个函数等价类的最优电路成本达到11个门,这些最大复杂度的函数代表了4输入2输出布尔函数中的极端案例。对于这些难题,研究不仅给出了上界,也充分论证了下界的合理性,有力推动了该领域的理论发展。

为了保证结果的准确性,作者设计了验证机制,运行简化程序遍历所有42亿多函数,验证了所得电路确实实现了对应布尔功能。虽然验证最优性本身具有难度,要求其他团队以不同算法独立复核,但作者后续的更高效代码已重复得到一致结论,增强了结果的可信度。4输入2输出布尔电路的研究不仅对理论电路设计具有深远意义,也为实际数字系统的逻辑优化提供坚实基础。优化电路门数能直接影响芯片功耗、速度和面积,尤其是在高性能计算和嵌入式系统领域。因此,该研究成果具备潜在的工程应用价值。与此前Knuth在2005年对5输入1输出布尔函数的类似研究相比,本次研究采用了更为精细的群论和搜索技术,在实际运算量上实现了突破。

对比中5输入函数群大小为7680,4输入2输出群大小为3072,群的不同导致等价类数量和结构发生变化,影响电路设计的复杂度和优化难度。除了理论贡献,作者还发布了相关数据库资源,便于其他研究人员和工程师查询最优电路设计方案,推动了工具和算法的普及应用。该数据库所需内存相对较小,设计的半完美哈希结构使得查询效率极高,有效支撑大规模布尔函数优化任务。未来,相关研究可能延伸到更多输入输出组合、更复杂的门库函数,甚至融合机器学习技术,进一步缩短设计时间,提升电路性能。同时,这也为研究离散数学、组合优化及计算复杂性理论的学者带来了丰富素材。综上,2020年对4输入2输出布尔电路最优设计的研究标志着布尔逻辑电路优化领域的重要进步,展现了高性能计算与数学理论结合赋能数字设计的典范。

随着技术的不断演进,这一成果将在数字集成电路开发和智能硬件创新中发挥愈加关键的作用,为打造更高效、更智能的电子设备奠定基础。