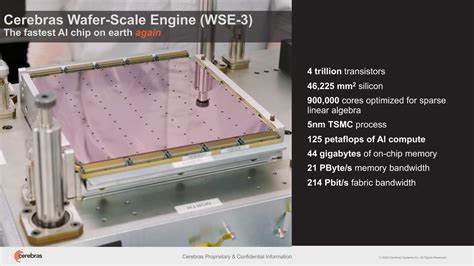

随着人工智能技术的迅猛发展,计算需求不断升级,传统芯片架构已逐渐难以满足复杂模型训练和推理的海量计算需求。在此背景下,晶圆级AI加速器(wafer-scale AI accelerators)作为一种创新硬件解决方案,凭借其卓越的性能表现、高效率运行和合理的成本优势,成为推动AI算力进步的重要力量。晶圆级AI加速器以其大规模集成和高度并行的设计理念,打破了单芯片面积限制,直接在整张晶圆上构建超大规模计算单元,显著提升计算密度和数据传输效率,从而有效解决传统多芯片系统中的带宽瓶颈和延迟问题。 晶圆级AI加速器的性能优势首先体现在其惊人的算力规模上。通过将数十亿乃至上千亿个晶体管集成于单一晶圆,实现了难以置信的计算核心数量与连接密度。这种规模的扩展不仅使得每秒浮点运算次数(FLOPS)大幅提升,还极大增强了模型并行处理能力,满足复杂神经网络的巨大数据吞吐需求。

相比传统GPU或多芯片系统,晶圆级设计通过消除芯片间的物理界面带来的通信延迟,提高了整体系统的同步效率和任务分配精度。 在能效方面,晶圆级AI加速器同样具有显著优势。由于其超大规模集成特点,使得更多的核心能够共享电源供应和散热资源,从而降低了能量消耗。此外,这种设计能够实现更优化的数据本地存储和传输路径,减少了数据在不同计算单元间移动所耗费的能量。通过集成先进的低功耗工艺技术和智能调度机制,晶圆级加速器不仅提升了每瓦性能,还有效延长了设备整体寿命,彰显出极高的可持续发展潜力。 成本分析则展现了晶圆级AI加速器在投资回报率上的独特竞争力。

初期制造晶圆级芯片所需的工艺复杂且成本较高,但由于单晶圆芯片所提供的超大计算资源,大幅减少了对多芯片系统和复杂互联结构的依赖,降低了整体系统设计和维护的复杂度。同时,晶圆级加速器能显著缩短开发周期和系统调试时间,降低了工程投入成本。长期来看,其高性能和高效率带来的更低电力消耗与空间占用,进一步减少了运营成本,加快了人工智能应用的商业化落地步伐。 晶圆级AI加速器在设计实现过程中,面临诸多技术挑战。首先是制造难度,从晶圆尺寸的完整制备到芯片内部核心的连接,必须保证极高的良率和一致性。任何一个制造缺陷都可能导致整块晶圆的性能锐减或失效。

其次是热管理问题,大规模的集成电路产生的热量集中且密度高,如何高效散热成为稳定运行的关键。此外,芯片内的复杂通信架构需支持超高速数据传输且保证低延迟,这对设计提出了极高的要求。针对这些挑战,业界不断推进先进制造工艺、创新冷却系统和智能互连技术的发展。 应用层面,晶圆级AI加速器适用于要求极高算力和实时响应的场景,如大型语言模型训练、高精度图像识别、自动驾驶系统的多传感器融合及复杂物理模拟等领域。在云计算平台和超级计算机中,晶圆级加速器能够极大提升模型训练速度,缩短开发周期,同时通过高能源效率实现生态友好型计算布局。边缘计算设备也借助其高性能集成优势,实现推理任务的本地化处理,降低数据传输延迟和安全风险。

未来,随着制造工艺的不断提升和设计架构的日趋成熟,晶圆级AI加速器有望实现更大规模的集成度、更低的能耗比和更灵活的适应性。人工智能的多样化发展需求将推动相关硬件设计向异构计算、可重构架构以及AI专用优化方向发展,从而进一步释放晶圆级加速器的潜力。其跨越式的性能提升和高效成本控制,将助力更多企业和研究机构打造面向未来的智能计算基础设施,引领AI技术进入新时代。未来在人工智能芯片的进化道路中,晶圆级AI加速器无疑将扮演不可替代的角色,驱动行业创新,实现智慧社会的全面升级。