随着半导体工艺的不断进步和应用需求的多样化,数字电路设计面临着愈发严苛的性能、功耗和面积挑战。逻辑综合作为设计流程中将高层次描述转换为硬件实现的关键步骤,其优化能力直接决定了最终芯片的质量。传统逻辑综合方法多依赖启发式规则和局部优化,难以全面探索设计空间,导致性能提升受限。近年来,基于平等饱和(Equality Saturation,简称e-饱和)的优化技术逐渐兴起,为逻辑综合带来了全新的思路。E-饱和通过维护包含所有等价电路变换的图结构,能够在一次构建过程中汇聚大量可能的表达式形式,实现结构的广泛探索与重写,显著提升了优化的深度和质量。然而,受限于图结构的复杂性和计算资源,e-饱和在大规模电路上的扩展性一直是业界关注的难点。

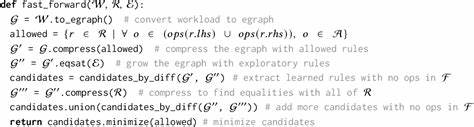

针对这一瓶颈,E-morphic框架的提出为逻辑综合领域注入了新的活力。它是首个将e-饱和应用于技术无关优化后的结构重综合过程的系统化工具,支持在技术映射之前对电路结构进行深入的重写和重构。E-morphic通过多项关键创新实现了卓越的可扩展性和提取效率。首先,其支持直接将e-图转换为电路结构,避免了传统繁琐的中间步骤,简化了流程并节省了计算资源。其次,E-morphic通过精妙的解空间剪枝技术,有效剔除冗余和不利的优化路径,确保资源集中于高价值的变换上。这一点极大提升了整体处理效率。

此外,引入模拟退火算法进行e-图提取,赋予系统避免局部最优解的能力,在复杂设计空间中找到更优的结构实现。 这些技术的融合使得E-morphic不仅提升了e-饱和的执行速度和结果质量,同时也缓解了传统逻辑综合过程中存在的结构偏差问题。结构偏差常导致优化过程过度依赖原始电路形态,限制了可能的性能突破。借助并行化的结构探索和重综合流程,E-morphic能更全面地利用设计空间,发掘潜在的高效电路结构,实现性能与面积的双重优化。 从实验结果来看,E-morphic在国际知名的EPFL大规模基准电路上表现出色,较主流的ABC延迟优化流程平均节省了12.54%的面积,并带来了7.29%的延迟缩减。这不仅体现了E-morphic强大的实际应用价值,也预示着基于平等饱和的结构探索有望在未来芯片设计中扮演关键角色。

随着架构复杂度持续提升和新型设计需求的涌现,这种方法的可扩展性优势尤为重要,能够支持更大规模电路的优化,助力业界迎接更多挑战。 逻辑综合的未来发展趋势中,结构探索将持续被视为关键突破口。基于传统方法难以兼顾效率与质量,E-morphic体现了新兴算法与计算策略结合的典范。其核心思想强调通过数学上的等价验证和智能搜索算法,找到最佳的结构替代,从而在保证功能正确性的前提下最大化性能空间的利用率。该方法在逻辑综合之外,也为相关领域如形式验证、量子电路优化等提供了重要启发和技术借鉴。 此外,E-morphic框架的设计理念也具有较强的开放性和适应性。

随着人工智能和机器学习技术的发展,将智能引导的搜索策略与e-饱和结合,可以进一步提升优化效果和自动化水平。未来在工业级设计工具链中的集成,更有望推动低功耗、高性能芯片的定制化设计,实现从设计理念到硅片制造的高效闭环。 总的来看,基于可扩展的平等饱和技术,尤其是E-morphic框架的实践,为逻辑综合带来了革命性的进展。它不仅优化了电路的结构和性能,也为设计师提供了更灵活高效的优化手段。随着此类技术的不断完善和推广,逻辑综合领域的创新步伐必将加快,助力推动整个集成电路产业迈向更加智能化和高效化的新阶段。