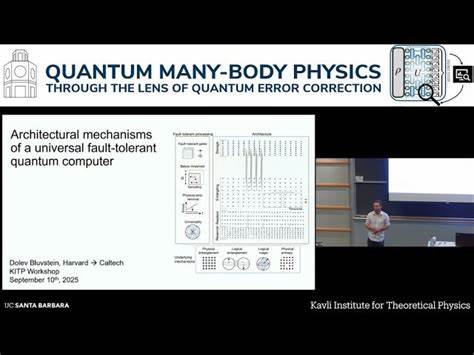

随着量子计算技术的不断进步,通用且具备容错能力的量子计算机成为科研前沿的核心目标。量子计算机拥有强大的并行计算能力和处理传统计算机无法胜任问题的潜力,尤其在化学模拟、优化问题和密码学领域。然而,量子比特的脆弱性和受环境干扰影响的特点,成为实现大规模量子计算的重大挑战。如何设计高效、稳定且可扩展的量子计算架构,是推动量子技术迈向实用化的关键所在。近期,利用多达448个中性原子的可重构阵列,科学家们突破传统限制,展示了一套完整的通用容错量子处理架构,并深入探索其背后的物理机制。这种创新性方法不仅结合了量子纠错代码和深度逻辑门操作,还通过跨尺度的量子态传输实现了逻辑的普适性,极大提升了量子计算的容错阈值和计算效率。

量子纠错是实现在错误频发的环境中维持稳定量子信息的基石。其中,表面码作为当前研究的热点,通过局域性的测量和反馈循环,有效抑制了量子比特的失误。此次实验通过四轮重复的表面码量子纠错流程,借助原子丢失检测和机器学习译码技术,实现了约两倍于阈值的性能改善。这表明系统能够识别并纠正大部分误差,显著延长了有效量子计算时间。除此之外,逻辑纠缠的产生和操控是量子算法中不可或缺的元素。研究团队利用横向逻辑门和晶格手术方法创建了高质量的逻辑纠缠态。

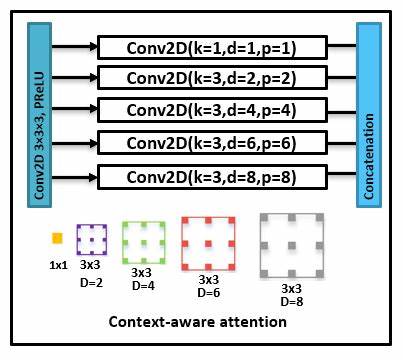

通过跨逻辑量子比特的操作,实现了多体量子态的精准调控。创新之处在于,结合三维量子编码[[15,1,3]],推广了逻辑传输门和任意角度门合成策略,将量子逻辑的普适性推向一个新的高度。这允许在保证低资源消耗的情况下,实现复杂的量子操作序列,满足了未来量子算法对灵活性的多样需求。另一项重大突破在于中途电路中量子比特的重复利用。这种技术大幅度提高了实验循环速度,提升了量子态制备和测量的效率。实验中,通过[[7,1,3]]和[[16,6,4]]等高效编码方案,允许深层电路的反复运作,支持数十个逻辑量子比特和数百次逻辑传输动作。

与此同时,系统内部的熵值保持恒定,确保了量子信息的纯净性和计算的连续稳定。本次研究还揭示了量子逻辑与熵管理之间的内在联系。利用物理纠缠资源合理构建逻辑门和生成"魔术态",为复杂量子门的实现打下基础。同时,基于量子传输的逻辑门设计,不仅确保了操作的容错性,还实现了物理量子比特的快速复位功能。这样的设计极大减少了物理成本,提高了架构的实用性和扩展性。该研究为量子计算体系结构设计提供了重要指导。

通过集成先进的量子纠错技术、灵活的逻辑门设计和高效的资源管理,构建了一套兼顾稳定性与效率的量子计算平台。基于中性原子系统的硬件优势,如高致密度排列和可重构能力,展示了量子计算从实验室向工业化迈进的可能路径。展望未来,随着此类架构技术的不断完善,通用且容错的量子计算机将逐步实现,助力解决传统计算难以触及的复杂问题。持续深化量子纠错理论、优化逻辑门实现方式以及提高量子比特的物理性能,将成为推动量子计算技术商用的关键动力。通过全球科研团队的协作,量子计算有望在不远的将来进入实际应用阶段,迎来计算领域的重大变革。 。