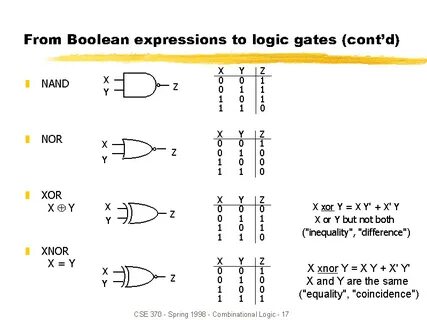

在计算机科学和图论领域,传递闭包的计算是一个基础而重要的问题。传递闭包用于描述图中节点之间通过路径可达性的关系,是路径分析、数据库优化、程序分析等多种领域的核心操作。对于节点规模不大的图,尤其是最多8个节点的小型图,传统算法的效率并不是瓶颈,但如何利用现代处理器架构特性和位运算技巧,极大提升计算性能,成为热门研究方向。本文将从布尔逻辑的基本概念出发,逐步深入到利用位运算和SIMD指令集实现微型图的传递闭包计算,解析每种方法的原理与优化策略,帮助读者理解高效实现的细节所在。 最直接理解传递闭包的方式是通过Warshall算法,其本质是对图的布尔邻接矩阵进行迭代更新,使得最终矩阵表达了任意两点之间的可达性。在节点数为8的图中,可以将8×8的布尔矩阵映射为一个64位无符号整数,每一位对应图中一条潜在的边。

相比传统二维数组,该位压缩方式不仅节省内存,也具备了位并行操作的潜力。 传统的Warshall实现中,算法需要三层循环,每次判断是否存在从节点i通过节点k到节点j的路径并更新邻接关系。在C++中,用std::bitset<64>表示图的邻接矩阵,代码易读,但执行效率有限,尤其是在条件判断和逐位更新中存在大量流水线瓶颈。此外,单个位操作次数多,无法充分利用CPU的宽字长寄存器和向量指令优势。 接下来,优化思路的核心在于充分利用位运算的特性,减少分支判断,提升并行处理能力。一个重要的“技巧”是提取第k行的所有边(即k节点出发的所有邻居),并根据行k中某一位为1的信息批量合并到第i行。

具体来说,如果节点i能直接到达节点k,那么将第k行的边集合整体通过位移加入第i行,达到路径合成的效果。这种方法避免了对每个元素反复判断,转而利用一次位掩码乘法完成批量条件赋值。 进一步优化中,将中间变量设为循环外捕获的旧状态副本,避免因边更新导致的条件判断误用最新数据,保证算法收敛的正确性。这一步虽然增加了一些内存开销,但显著提升了编译器针对循环优化的可能性,使得整体性能提升可观。 其中,最具代表性的优化版本巧妙利用了字节中最低有效位的掩码,通过移位和乘法实现一次性更新多个节点的邻接情况。精妙之处在于,一个64位整数可以看成8个字节,每个字节最低位表示一个布尔标志,乘以第k行的边集合后,非零的字节被扩展为完整的字节,从而实现条件批量赋值。

这种位级并行的设计极大缩短了执行路径,减少分支预测失败带来的性能损失。 与传统布尔矩阵乘法不同,MMIX体系结构上的MOR操作提供了灵感。MOR操作在字节化布尔矩阵乘法基础上,通过字节掩码和移位实现了高度并行的矩阵乘法,能够一次性处理八行数据,这为进一步优化传递闭包运算提供了理论支持。虽然MOR不是直接适用于所有硬件,但通过模拟和与后续的位运算技巧结合,可以实现高性能的小图传递闭包计算。 在高性能计算时代,SIMD(单指令多数据)成为提升批量数据处理速度的利器。针对8节点图的转移闭包问题,利用AVX2指令集能够一次处理多个图的传递闭包。

具体做法是将多个64位图掩码打包进256位寄存器,针对每个节点的传递关系,使用SIMD内置的移位和混合字节指令,同时更新多个图状态,从而实现指数级的性能提升。这种批处理思路非常适合应用在大规模图集合分析、状态空间搜索和动态规划等场景。 AVX-512同样能够扩展这一思路,提升单次指令宽度至512位,理论上处理8~16个图。但由于AVX-512指令的实现细节差异,诸如缺乏对应的vpblendvb指令,需要巧妙设计替代方案,比如利用特殊掩码混合指令和测试指令的结合。尽管如此,在实际测试中基于AVX-512的改良版本在吞吐量和延迟方面的表现优于标量代码,却仍未达到理论的最大性能,从而提示了硬件指令集与算法适配之间存在的微妙平衡。 实际应用中,图的大小大多超过8节点,直接应用上述位运算技术显得不切实际。

然而,对于状态有限且需要高速推演的微型图,以上方法提供了极具价值的性能基线。尤其是在嵌入式设备、加密算法分析、程序静态分析以及数据库索引优化等领域,这些技术能够结合领域特色,发挥关键作用。 总结来看,布尔矩阵乘法的本质与计算机硬件处理逻辑息息相关。通过将图的传递闭包计算映射到位运算和SIMD指令,不仅实现了算法的加速,还推动了理论与实用技术的结合。针对具体硬件平台的微调和优化,是提升性能的关键环节。未来,结合机器学习自动调整指令序列以及多核异构计算架构,针对图论算法设计定制化硬件指令,值得持续关注。

对开发者而言,理解传递闭包的位级优化手段,不仅能够提升自身代码性能,还可拓宽对现代计算机架构的认知,带来更广泛的软件设计思路。无论是位运算的巧妙利用,还是SIMD流水线的批量处理,都彰显了计算机科学中数学逻辑与硬件特征协同演进的魅力。掌握这些技术,能够在日益复杂的计算环境中游刃有余,应对各种挑战,实现高效而准确的图算法处理。