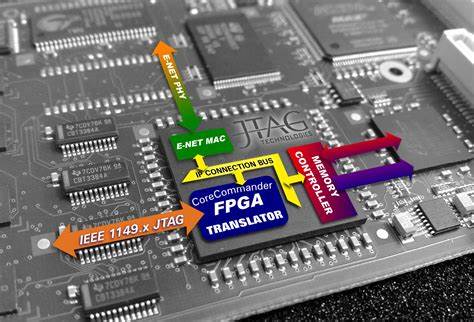

在FPGA设计领域,简单的外部按键操作却时常被低估其潜在风险。一个看似普通的按钮按下动作,实际上可能成为导致整个FPGA系统崩溃的导火索。理解为何如此简单的输入能引发复杂的问题,以及如何通过科学设计避免这些问题,是每一位FPGA工程师必须掌握的基础。首先,外部按键属于异步输入信号,它们与内部时钟域没有任何时序关系,这带来了一系列的挑战。按键本身的状态变化是随意的,不受FPGA内部时钟控制,正因如此,当外部按键信号在内部时钟采样的边缘附近变化时,会发生所谓的亚稳态现象。亚稳态指的是触发器或寄存器在时钟边沿采样瞬间,因输入信号未稳定而进入一种既不是明确高电平也不是低电平的非确定状态。

此状态如果未及时释放,可能导致整个系统逻辑异常,触发错误或者不可预知的行为,这是导致FPGA系统崩溃的关键技术根源。除了亚稳态问题,机械按键本身还存在机械抖动现象。当按键被按下或松开时,金属触点会快速多次接合和断开,导致信号线呈现出多次快速切换,这种波动可能持续数毫秒。若直接将此未经滤波的信号输入FPGA,系统会误判为多次按键事件,从而产生错误逻辑响应甚至系统故障。因此,解决异步按键信号的首要难题是有效同步外部信号,消除机械抖动,从而在FPGA内部形成稳定、可预测的输入状态。针对亚稳态问题,业内普遍采用多级同步器设计。

多级同步器通过级联多个触发器,将异步输入信号逐级同步到内部时钟域,降低亚稳态在下游逻辑传播的风险。具体来说,信号先经过第一级触发器采样,进入短暂的等待期后再传递到第二级触发器,通常采用三阶触发器配置即可极大提升系统的平均无故障时间(MTBF),并降低亚稳态引发错误的概率。设计时应利用同步触发器特有的工具属性(例如ASIC或FPGA综合工具中的ASYNC_REG属性),以告知工具该触发器用于异步输入同步,帮助优化布局布线及时序约束,避免因综合工具误判而漏失保护机制。机械抖动的消除则通常采用数字消抖电路。实现方案多样,但以基于移位寄存器的延时滤波器最为广泛和简单有效。在此方案中,按键同步信号经过一个长度较长的移位寄存器链,仅当寄存器链中所有寄存器均显示按键为按下状态时,才认定按键被稳定按下。

此设计借助时钟边沿逐步延迟输入信号,滤除短暂的波动信号。合理选择移位寄存器的长度能确保消抖时间满足机械触点变化的实际需求,通常工控级别设计会选择微秒甚至毫秒级别的消抖时间来提升可靠性。除了多级同步与数字消抖,FPGA中的时钟管理模块(如MMCM或PLL)同样发挥着至关重要作用。它们不仅负责将外部系统时钟频率转换为内部逻辑所需的精确时钟信号,还能生成稳定的时钟域用于同步和流水线操作。确保时钟源的稳定及锁定信号的同步至关重要,否则时钟波动将传递至逻辑模块,掩盖同步信号的稳定性,潜在导致系统整体异常。理想的设计中,时钟锁定信号自身也需通过多级同步进行处理,确保系统处于稳定的时钟环境中开始其他操作。

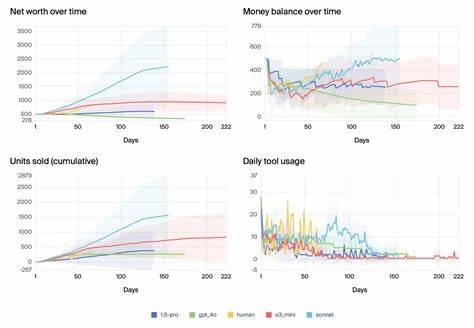

这种严格的时钟及复位同步机制,是保证FPGA系统稳定的基础。在设计实战中,结合多级同步及数字消抖模块设计,形成一个模块化、参数化的架构尤为重要。通过参数化同步阶段数、多位同步宽度以及消抖寄存器长度,设计人员能够根据具体应用需求灵活调整,达到最佳的性能与资源占用平衡。同时保持良好的编码风格和模块封装,利于代码复用和维护。仿真验证及时序分析是设计流程中不可或缺环节。通过搭建系统顶层测试平台,采用时钟驱动和按键信号激励,模拟实际异步信号变化,验证同步电路能稳定捕获信号且消除抖动,同时对时序约束进行详尽分析,确保设计满足各项时序规范,杜绝产生亚稳态风险。

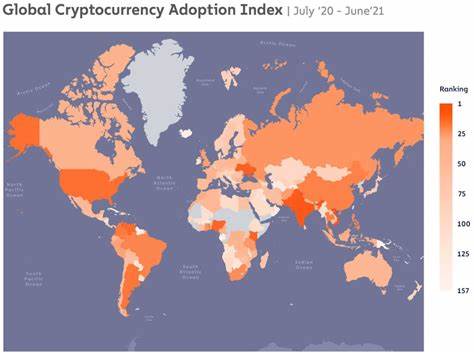

在实际工程中,忽视异步信号的正确处理常导致调试困难、系统偶发性故障和可靠性低下。尤其是在安全关键、工业控制以及汽车电子等领域,按键输入的错误处理可能带来致命后果。因而,掌握异步信号同步技术与数字消抖技术,结合精准的时钟管理方案,是构建高可靠FPGA数字系统的基石。未来,随着FPGA在人工智能、物联网、嵌入式系统等新兴领域的广泛应用,面对更多异构信号、多时钟域互联的复杂设计,异步信号同步和消抖技术将进一步升级。多位宽度同步、多域FIFO、灰码编码及握手机制等高级同步技术将成为主流。同时,配合先进的硬件验证工具与静态时序分析,不断提升系统健壮性与容错能力。

总之,面对简单按键可能带来的复杂系统崩溃风险,FPGA设计师需从根本上理解异步信号特性,采用科学严谨的多级同步和数字消抖技术,辅以规范的时钟管理和全面的设计验证,方能打造稳定、安全、可靠的数字硬件系统。只有如此,才能真正将技术优势转化为产品竞争力,实现FPGA设计的高质量、高可靠性目标。