在现代数字芯片设计的浩繁世界中,静态时序分析工具(简称STA)默默地扮演着至关重要的角色。尽管它不像综合工具那样广为人知,但其作用却关乎芯片的性能和功能是否真正达标。芯片设计不仅仅是逻辑的堆叠,更是电子信号及其时序的精细处理,而STA正是这个时序保障体系中的核心守护者。它的诞生与1960年代的项目管理方法——项目评审技术(PERT)紧密相关,那时工程师们通过分析任务的关键路径和缓冲时间来管理复杂项目,而STA则把这一思想搬到了芯片设计领域,帮助工程师识别电路的关键时序路径及潜在的延迟隐患。现代STA工具,如Synopsys PrimeTime或Cadence Tempus,尽管名字不同,但其核心使命一致:确保芯片内部信号能够按时到达,使整个系统能够正确同步运行。芯片设计人员一般会使用硬件描述语言(HDL)如Verilog来描述数字电路的功能与结构,但STA工具不能直接理解这些“潮流语言”。

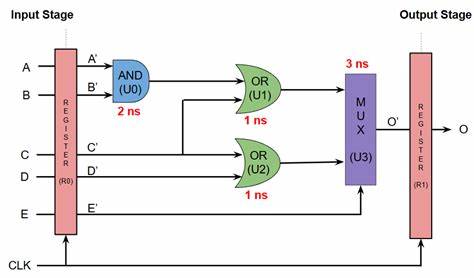

相反,STA只能处理数字设计转化后的“网表”(Netlist) — 这是一份详细列出电路中各种元件(包括逻辑门、复用器、存储单元等)以及它们间连线的清单。综合工具负责把高级的HDL代码转换成STA能够理解的网表,而STA则从物理实现的角度出发,评估电路中信号的传播延迟及其对整体时序的影响。芯片不同于纯软件,变化发生的速度远超过人眼所能感知,然而电子信号的流动终究受限于物理规律,光速虽快,仍无法瞬间穿越一块面积不断扩增的硅片。每个逻辑元件都会增加微小的延迟,这些延迟积累起来,可能导致最终结果错过时序窗口,致使芯片功能异常。STA正是为了解决这个问题而存在的。分析芯片的各条信号路径上累积的延迟是否满足设计的时钟周期约束,并判定芯片能否按预期稳定运行。

芯片设计中的“同步”概念尤为重要。设计人员通常通过周期性的时钟信号将芯片划分为多个阶段,使数据在某个时钟沿(通常是上升沿)时被统一“采样”和存储。这样,虽然每条信号路径的延迟不同,时钟周期的存在则为数据输送设定了一个统一的节奏,在每次时钟事件发生时保证数据稳定且正确。然而,使用同步机制并不是解决时序问题的一劳永逸。寄存器作为存储单元,必须满足严格的时间要求,包括“建立时间”和“保持时间”。建立时间指的是数据在时钟事件之前必须保持稳定的最短时间,否则寄存器可能无法正确读取数据。

保持时间则要求数据在时钟事件后仍需保持一段时间不变,以确保读取的正确性。这些时间约束受限于电子元件的物理属性,是设计中不可忽视的细节。除了这些,寄存器本身也存在传播延迟,其中包含时钟到输出的延迟和数据到输出的延迟,而STA需要考虑这一切细节,才能准确判断时序是否满足约束。静态时序分析的核心任务,就是对芯片中每条可能的信号路径进行延迟计算和约束检查。通过对寄存器输入端和输出端信号传递路径上的延迟进行求和,并与时钟周期及建立/保持时间进行比较,STA能找出所有时序满足与否的路径。如果路径的总延迟小于时钟周期减去建立时间,则该路径的“正余量”或“正Slack”表示有余裕;如果延迟超出该范围,则为“负Slack”,意味着时序失败。

负Slack路径可能导致芯片出现数据错误或功能异常,必须被设计者及时识别并优化。在实际应用中,STA不仅帮助芯片设计验证,也指导设计优化。设计人员可以根据STA反馈调整逻辑路径、优化布局或调整时钟策略,进而提升芯片性能和稳定性。而且,STA还能检测“保持时间”违规,当数据变化速度过快导致寄存器无法正确锁存时,这种问题同样需引起重视。总之,静态时序分析工具以其精准预测和细致检查,为芯片从设计蓝图到硅片制造的转变保驾护航,避免昂贵的设计返工和质量隐患。随着芯片工艺复杂度提升和设计规模扩大,STA的作用只会更加重要。

掌握STA的原理和应用,已经成为现代芯片工程师必备的技能之一。它将复杂的物理世界和抽象的数字逻辑之间架起了一座桥梁,让设计从电路图纸走向现实中的高速运算。