量子计算作为现代科学技术的重要前沿之一,正以惊人的速度发展。特别是超导量子处理器,凭借其成熟的制造工艺和良好的可控性,成为通用量子计算领域的先锋。然而,随着量子比特数量的增加,超导量子处理器面临着频率拥挤、线路复杂及封装限制等多重挑战,使得单芯片大规模集成变得异常困难。为解决此难题,分布式量子计算架构应运而生,通过连接多个小规模但功能完备的量子处理器,构建更具扩展性的量子计算系统。其中,实现远程量子比特之间的高保真两比特纠缠门,是实现分布式量子计算的核心要素和技术瓶颈。近期的一项突破性研究成功展示了通过基于驻波模式的30厘米超导同轴电缆连接两台远程量子处理器,实现了高保真的受控非门(cnot)和受控相门(cz),该成果为未来大型量子计算系统搭建注入了强劲动力。

实验中每个量子处理器均封装于独立金属盒中,内部集成可调谐频率的跨导晶体管(transmon)量子比特、读出谐振腔以及半波长的共面波导结构。两台处理器通过一条精心设计的15次电流驻波模式连接的超导铝制同轴电缆实现无损耦合,有效减小了由连接点引入的信号损耗与噪声影响。系统整体被置于低温稀释制冷机中,通过磁通线圈对量子比特频率精确调谐,确保耦合模式的最佳匹配以及残余交叉耦合的最小化。理论上,系统可用包含多模式的哈密顿量描述,基于达菲振荡子模型,载流波模式为介导量子比特间交互的媒介。数值模拟证明在分散耦合区内,选择合适的工作频率可以实现强耦合与抑制不必要相互作用的平衡,使得交叉频率驱动(cross-resonance,CR)效应得以高效激发。CR门作为固定频率超导量子比特系统中常用的纠缠门类型,利用一个量子比特的驱动微波信号诱导另一个量子比特产生条件性旋转,实现两比特量子门。

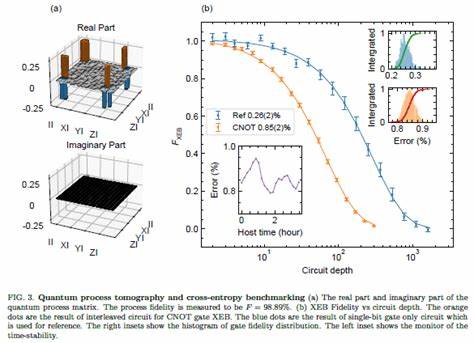

在该远程系统中,通过微波脉冲精确控制CR驱动的幅度和频率,成功消除了多余的非目标相互作用,实现了清晰的cnot门操作,门长仅为204纳秒,保真度达到了99.15%。此外,通过对两量子比特同时施加频率特定的驱动信号,实现了基于条件相位累积机制的cz门,门操作时间为430纳秒,保真度同样达到98.03%。这两个高性能远程纠缠门不仅不需要额外的辅助量子比特,也避免了复杂且耗时的反馈控制流程,极大提升了系统的硬件效率和延迟特性。为客观评估量子门操作性能,研究团队采用了包括量子过程层析(QPT)和交叉熵基准测试(XEB)两种技术。QPT有效重构了实验量子门的过程矩阵,对比理想模型,揭示门的完整动力学特性;而XEB则以其强鲁棒性和免受状态制备与测量误差影响的优势,提供了高精度的门保真度测量。多次独立测试结果表明,该体系远程cnot和cz门均具备顶尖的性能参数,且表现出稳定的时间特性,预示了其在实际量子计算任务中的可靠应用。

为了进一步验证远程纠缠的真实性,研究人员设计并完成了遥距贝尔不等式测量,成功制备出贝尔态,测量结果以3.8个标准差显著超过经典极限,且在经过测量误差校正后,相关系数逼近量子极限,彰显了系统的量子纠缠质量与控制精度。整个实验系统的成功得益于精密设计的量子硬件接口、细致的参数调优以及先进的微波控制技术。驻波模式的利用不仅提升了量子比特间相互作用的强度和选择性,还显著抑制了通道损耗与多余模式耦合,保障了较长距离传输中的信息完整性。该实现代表了通用分布式量子计算架构中实现两量子比特门的里程碑,突破了传统基于飞行光子或辅助谐振腔的量子态转移方法在面对量子叠加态时的操作限制和非单元性问题。未来,该技术有望扩展至多个量子处理器之间的网络化连接,实现更大规模的量子纠缠分发和复杂量子算法的并行执行。与此同时,硬件效率的提升也为量子误差校正码的高密度实现提供了有力支持,推动了实用量子计算机向真正量子优势的阶段跃迁。

尽管当前实验成果已取得显著进展,但仍存在进一步提升空间,包括降低环境噪声影响、拓展量子比特数量以及提升系统整体的容错能力。未来的研究或将聚焦于多模式耦合的更深层次控制、高速反馈机制集成以及优化型量子控制脉冲设计。此外,结合动态调谐技术与量子网络协议的创新,也将助力实现更加灵活且可扩展的分布式量子计算架构。总体来看,远程超导量子处理器之间的完美纠缠门实现,不仅破解了超导量子计算扩展性难题,也为量子信息处理体系结构设计提供了崭新思路,为联盟量子计算和量子互联网的发展奠定了坚实基础。随着技术的成熟和工程挑战的逐步克服,分布式高保真纠缠门将在未来超导量子计算生态中发挥核心作用,推动量子技术产业化和商业化朝着更广阔的方向发展。 。