在计算机科学的发展历程中,CPU架构的演变一直是技术创新的焦点,特别是那些奇特而不走寻常路的设计,往往展现了工程师们对计算本质的独到理解和突破。2020年,一款名为"仅靠MOV指令运转的CPU"设计引起了极大关注,这种基于运输触发架构(Transport Triggered Architecture,简称TTA)的CPU,以其极简的指令集和独特的实现方式,重新诠释了CPU设计的可能性。本文将深度探讨这一奇异CPU架构背后的思想脉络,解读其设计细节,并分析其优势与局限,助您全面了解这款非凡的计算机核心。 传统CPU架构通常依赖于丰富的指令集与内部寄存器组合,通过多种算术逻辑单元(ALU)和寄存器的协同工作,完成复杂的计算任务。而运输触发架构的创意在于将计算实体几乎全部映射到存储单元,通过单一的"移动(MOV)"指令,把数据从一个存储地址传送到另一个,实现所有计算和控制逻辑。换言之,不需要专门的计算指令,简单的"数据搬运"本身就承担了计算职责。

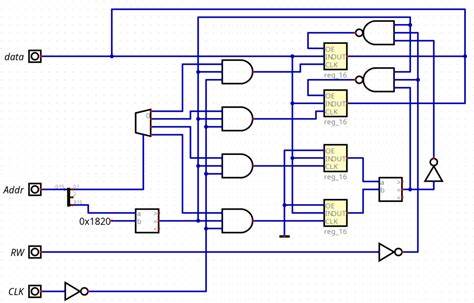

这种架构的核心理念在于"触发器即传输",即通过将运算操作视为数据传送到特定硬件模块(如算术逻辑单元的输入端口)来触发相对应的处理。比如,将两个操作数依次传输至ALU的两个输入端后,ALU自动对其执行加法操作,结果存储在对应输出寄存器,随后通过MOV指令传回目标内存地址完成保存。 为了实现这样的设计,所有关键组件包括ALU、程序计数器、分支控制模块及通用寄存器均被内存映射。这种内存映射的设计确保了CPU无需显式执行复杂的指令,所有逻辑皆通过移动数据完成,同时简化了控制逻辑的实现。程序计数器作为内存中的一个特殊地址,通过移动新的地址值,便可实现程序跳转,支持条件和无条件跳转功能。 设计这一CPU的过程虽极简,但仍需要精心构筑多个关键模块。

首先需要一个能够分时调度操作流程的时钟分频器,将CPU的执行周期细分为四个时钟周期,分别用于取指令高16位(来源地址)、低16位(目标地址)、读取数据、写入数据四个步骤。时钟的节奏掌控着数据移动的流水线,实现同步和准确的操作。 程序计数器的实现基于一组74_161计数器芯片组成16位计数器,通过地址比较器判断是否需要加载跳转地址并更新计数器状态。设计中的比较器会监听特定写操作信号,识别写入程序计数器地址,允许程序动态修改执行路径。由于程序计数器也是内存映射的,程序跳转变得如同数据搬运一般简单直观。 算术逻辑单元则采用四个74_181 4位ALU芯片拼接组合,形成一个16位宽的运算单元。

为了保证数据传输的准确性,设计了相应的寄存器保存输入数据,同时通过总线驱动器控制数据传输方向,确保数据流不会反向干扰其他模块。简化设计使芯片数量最小化,硬件复杂度降到最低。 控制流模块为本设计添加了基本程序流程的判断功能。它由两个地址寄存器和两个数据寄存器组成,通过比较两个数据寄存器的值并依据比较结果选择返回地址,支持简单的条件分支控制。该模块使用了比较器和译码器逻辑,结合寄存器的地址映射来实现条件执行判断。这为该CPU实现了最基础的逻辑跳转和流程控制能力。

在外围设计中,还集成了GPIO模块用于观察输出和调试。GPIO模块通过内存映射的方式,直接保存写入的数据值,方便用户读取和监控程序运行状态。此外,整个CPU使用的是单总线结构,既包括了程序存储空间也包括了数据RAM,具备64KB的寻址能力,可满足基本程序的存储需求。 编写程序方面,由于指令集仅包含MOV指令,所有程序本质上都是一系列的内存地址传送操作。以计算斐波那契数列为例,程序会通过不断移动寄存器中的数据到ALU输入端触发加法操作,再将结果存回内存,从而依次生成数列。更复杂的逻辑如循环和条件跳转都通过移动数据到程序计数器实现,借助条件模块判断循环是否结束。

尽管指令繁多且程序长度较长,但在该架构下,功能实现却异常直观且易于追踪。 MOV指令唯一操作的CPU设计虽然极具创新,却也存在明显局限。相比现代复杂CPU,其执行速度较慢,每条指令需分四个时钟周期才能完成,计算密集型任务效率不高。且由于所有寄存器均映射内存,硬件资源利用率较低,小规模设计却占用较多芯片。另一方面,该设计却高度简化了控制逻辑,降低了设计难度,适合教学演示及探索计算模型原理。 总体而言,运输触发架构与传统CPU迥异,以"数据传送引发操作"为设计核心,为处理器设计带来了另类思考视角。

MOV-only CPU项目以其简洁的实现,展示了基于内存映射与单指令操作的CPU可行性,适合深入理解计算机内部工作机制和处理器设计理念。该设计不仅是学术和兴趣探索的典范,也激发了人们对未来CPU简化与极限设计的兴趣。 未来,类似的运输触发架构有望与FPGA等可编程硬件相结合,以实验和定制目的推广,从而实现低功耗、低成本的嵌入式处理器解决方案。尽管该架构目前仍属小众,但其独到的设计思想对计算机体系结构领域乃至硬件创新有着不可忽视的启迪作用。 。