随着数据中心计算规模的日益扩大,芯片稳定性与可靠性的重要性愈发凸显。尤其在超大规模数据中心中,静默数据错误(Silent Data Errors)成为亟待解决的挑战。这类错误因其发生概率极低而常常逃脱传统检测手段的关注,导致在实际运行过程中出现难以预料的性能异常和数据偏差。强化学习,作为人工智能的重要分支,通过自主学习和反馈调整,正为检测这些隐秘的芯片缺陷提供了一条全新的路径。静默数据错误的产生主要源于芯片制造过程中允许的微小差异。尽管每个晶体管均经过严格测试,但由于制造工艺的超高复杂度和极限尺度的物理特性,即使是微不足道的电性能波动,也可能在数以亿计的晶体管中累积,最终引发计算错误。

在大型数据中心,数百万节点同时运行,每秒数以亿计的计算操作形成海量数据,极小概率事件的发生频率被放大到可察觉的程度。传统测试方法如标准的质量控制和静态电路分析,虽能覆盖普通缺陷,却难以捕捉到这类由隐蔽硬件劣化和环境因素交互引发的错误。这些错误往往在芯片实际使用数月后才逐渐显现,带来的影响不容小觑。Intel工程师们开发了一种以强化学习为核心的检测技术,用以优化静默数据错误的识别效率。该方法基于一种称为Eigen测试的传统测试手段,通过矩阵乘法等复杂数学运算来激活潜在缺陷。然而,完整运行所有可能的Eigen测试需要耗费大量时间,因此工程师们采用强化学习引导测试选择,着力在有限测试周期内最大化错误发现率。

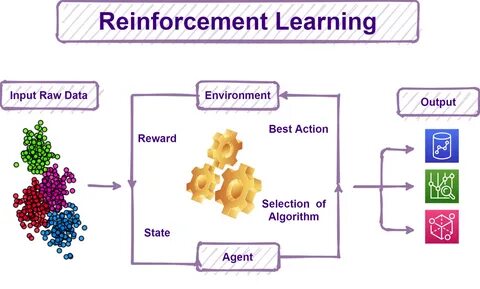

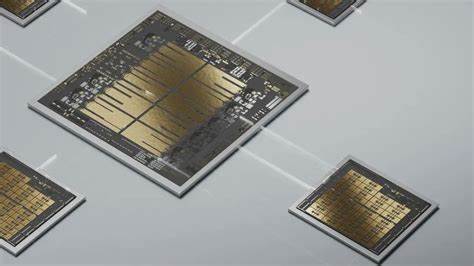

强化学习算法通过模拟环境与芯片交互,试验不同组合和参数的测试用例,取得成功检测的反馈则作为奖励信号回馈模型,促使算法不断调整其测试策略。经过数百次迭代,系统能够自主找出最适合激活缺陷的测试序列。这种方法特别针对芯片中大面积使用的融合乘加运算单元(FMA)区域,该区域因晶体管密集且电磁干扰影响广泛,容易暴露潜在隐患。传统测试难以涵盖多次通断电过程引发的动态缺陷,强化学习驱动的测试正弥补这一不足。通过改进的测试策略,Intel团队实现了检测效率较随机测试提升五倍的突破。对于巨大数据中心而言,提前识别并剔除静默数据错误芯片,可以显著降低故障率,提升计算精度以及系统整体可靠性。

同时,这一技术革新为芯片设计反馈环节提供了宝贵数据,助力优化制造工艺,预防未来批次产品中类似缺陷的产生。强化学习的优势不仅体现在芯片品质检测领域,也逐渐影响整个半导体产业的智能化趋势。随着芯片复杂度不断加大,手工设计和筛选测试方法的效率已难以满足需求。借助自动化、智能决策的强化学习算法,芯片厂商能够更快适应工艺变化,精准定位难以察觉的可靠性隐患。更重要的是,这种技术具备极强的可适应性。公开的Eigen测试套件配合强化学习,可被不同用户根据自身芯片架构和应用特点,定制化生成最优测试序列,极大拓展了检测手段的灵活度和效用。

未来,随着算法的持续进步以及芯片设计的不断革新,强化学习有望融入更多芯片研发和制造环节,实现设计缺陷预测、环境适应性评估,甚至动态故障修复等多维度智能优化。尽管制造业追求绝对完美始终是目标,但静默错误的不可避免性决定了早期发现和主动管理策略的重要性。基于强化学习的检测技术,正好为这一目标提供了科学且高效的解决方案。其背后的理念是通过数据驱动的反馈机制不断完善测试策略,实现对隐藏风险的最大化捕捉,从而提升微电子产品整体性能和寿命。在实际应用中,强化学习不仅减少了静默错误带来的风险,节约运维成本,更为海量计算系统提供了坚实的信赖基础。对企业而言,这意味着更少的宕机、更高的服务质量和更强的市场竞争力。

在数字经济和人工智能日益普及的当下,确保数据中心中计算设备的稳定可靠,既是技术挑战,更是产业持续健康发展的关键。强化学习不仅开启了一条识别和预防静默数据错误的新路径,也展示了智能算法赋能芯片制造的深远潜力。展望未来,这一领域的进一步突破,将促进从芯片设计到系统维护的全面智能化升级,推动信息技术基础设施迈向更高效、更可信赖的新时代。