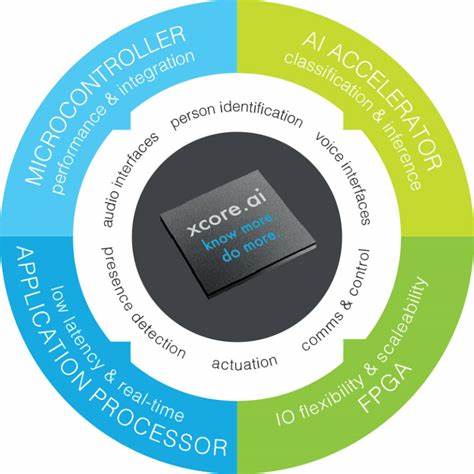

随着边缘计算和物联网技术的飞速发展,越来越多的人工智能推理任务开始在资源极其有限的微控制器上运行。所谓的边缘人工智能,其核心特点在于计算、内存和网络带宽的显著受限,而微控制器恰恰代表了这类极端受限硬件的典型范例。因此,理解微控制器上人工智能的具体工作机制,尤其是操作符(Operator)和内核(Kernel)如何协同完成推理任务,变得至关重要。本文将深入剖析这一过程,从模型权重的存在价值,到操作符定义及内核实现,再到硬件加速的多样化策略,全面呈现微控制器AI推理的真实面貌。 微控制器执行人工智能推理的第一步是加载和解析模型数据。以Tensorflow Lite Micro(以下简称tflite-micro)为主流推理运行时,其使用.tflite模型文件,该文件通过FlatBuffers格式封装。

与其他模型格式不同,tflite文件不仅存储模型参数(权重),还包括完整的计算图信息,也就是说模型中的每一步运算都由操作符定义,运行时通过读取计算图,逐步调用对应内核完成计算。操作符在这里相当于编程语言中的指令集,不同操作符代表矩阵乘法、加法、卷积等基本运算;内核则负责具体实现这些操作符的计算功能。 鉴于微控制器的资源受限,tflite-micro接口提供的操作符集相较于完整Tensorflow Lite大为精简。操作符的通用性与高效性成为关键考量点,因为每个操作符都必须能在尽可能有限的存储空间和计算周期内高效运行。以加法操作符(AddOp)为例,它既支持浮点数运算,也支持量化后的整数运算,其中量化版本可大幅降低存储和计算成本,体现出微控制器上人工智能推理不得不采用的优化策略。 具体来看,AddOp根据输出数据的类型不同,调用不同的内核函数。

例如在处理有符号8位整数(kTfLiteInt8)时,内核EvalAddQuantized会执行带量化参数的加法运算。量化过程包括输入数据的偏移调整、多倍数与移位操作,保证整数计算后结果仍符合浮点数等价的计算精度范围。更复杂的情况如广播(broadcasting)机制,允许不同形状的张量进行兼容运算,内核会采用慢速的广播版本函数来逐元素完成加法。这种内核实现形式是最基础且硬件无关的,任何微控制器都能运行,但效率相对较低。 为提升推理效率,微控制器厂商和开发者积极借助硬件扩展指令集,在内核实现中引入专门的加速函数。例如,ARM Cortex-M系列微控制器普遍支持DSP(数字信号处理)扩展以及新型的MVE(向量扩展,也称为Helium)指令集,这些特性能够大幅度并行处理矢量数据。

CMSIS-NN库充分利用这些扩展,提供了可选的内核实现,包括纯C实现、DSP指令优化实现与MVE指令优化实现。Tensorflow Lite Micro通过内核“移植”,集成CMSIS-NN的高效算子版本,使得相同的模型代码在支持这些扩展的芯片上运行速度提升数倍。 具体到加法操作,启用CMSIS-NN的EvalAddQuantizedInt8函数将调用arm_elementwise_add_s8接口。在带有MVE指令支持的硬件环境下,代码通过SIMD向量操作批量处理四个元素,利用向量加载、加法和重新量化等指令极大地减少循环次数和执行时间。而在仅有DSP扩展的环境,则通过打包偏移量及数据,使用特殊16位加法指令一次处理多个元素,兼顾效率与兼容性。底层代码根据编译宏自动选择最优路径,实现无需人工干预的性能提升。

除了利用核心指令集扩展优化,部分高端微控制器更搭载专用的神经网络处理单元(NPU),例如ARM的Ethos-U系列。通过专用NPU,整个推理任务中部分或全部操作能够完全放弃通用CPU执行,而由专用硬件单元完成,带来更高的速度和能耗效率。在Tensorflow Lite生态中,针对Ethos-U NPU的模型会经过Vela编译器转换。该编译器将模型中的多个基本操作连锁替换为单个自定义ETHOSU算子,包含紧凑化的命令流和硬件加速器访问地址。推理时,微控制器CPU仅需调用专用内核函数,通知NPU执行推理,极大减轻CPU负担。 尽管专用NPU提供强大性能优势,但其使用也带来兼容性挑战。

转为Ethos-U自定义算子后的模型无法在无此硬件支持的微控制器上运行,限制了模型移植的灵活性。相比之下,基于CMSIS-NN或纯C实现的内核,则兼顾通用性和性能,在设备生态多样的嵌入式领域显得更为实际和重要。 微控制器上的人工智能推理正处于从软件逐步适配硬件加速的关键阶段。操作符和内核的设计不仅决定了推理的功能完整性,也直接左右性能天花板。在模型转换、运行时加载与执行流程中,合理利用硬件特性和自主优化内核模块是提升推理效率、减少功耗和降低延迟的核心手段。随着芯片架构的发展及边缘AI应用的丰富,开发者需要掌握操作符的结构、内核实现细节与硬件加速选项,方能设计出适合目标设备且高效的AI解决方案。

未来,随着更多硬件扩展指令和加速器的出现,推理框架将继续演进,支持更广泛的操作符和优化路径。例如,更多类型的量化技术、多核并行计算调度、异构计算资源协同使用,都有望进一步提升微控制器AI的表现和适用性。同时,推理编译器的智能优化能力也将越来越关键,自动识别硬件特性并生成匹配内核,简化开发流程。开发者应持续关注Tensorflow Lite Micro和相关生态的发展动态,紧随技术趋势,确保所构建的AI应用能够在边缘设备上实现理想的性能和功耗平衡。 总的来说,微控制器上的AI推理是一个融合软硬件技术的系统工程。从模型到运营时环境的执行,操作符定义和内核实现环环相扣。

权重和计算图定义了模型结构,操作符充当了计算指令,而内核则是执行这些指令的具体算法和代码。通过引入架构扩展和加速库,实现了性能的质的提升。未来,随着边缘智能需求的增长,微控制器中AI的能力将日益成为智能设备的基础,带来更多创新和可能。