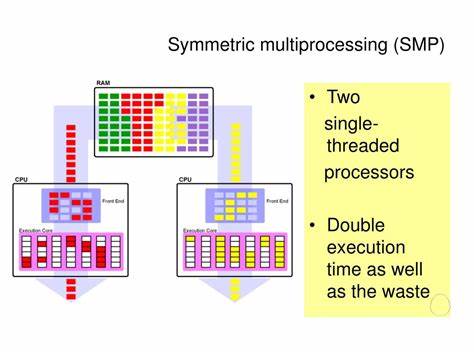

在现代计算机系统中,随着多核处理器的普及和多线程技术的发展,操作系统必须不断演进以充分利用硬件资源,实现更高效的任务调度和系统性能。Maestro操作系统作为一款正在开发中的多核支持操作系统,近期成功实现了对称多处理(SMP)功能,允许多核CPU并行运行并显著加快软件编译和执行速度。本篇围绕Maestro的SMP支持展开,详细分析其基于ACPI进行CPU核心枚举、APIC与PIC的中断管理差异、定时器校准、核心启动流程以及调度机制的实现,并探讨英特尔超线程技术对多核调度的影响与优化。对这些底层技术的理解不仅为内核开发者提供借鉴,也有助于提升普通开发者对多核架构调度原理的认识。 Maestro为了实现多核充分利用,首先需要识别系统中存在的所有CPU核心。这里ACPI(高级配置与电源管理接口)扮演了关键角色。

ACPI的MADT(多重APIC描述表)记录了系统中各个逻辑核心的本地APIC ID,这使得操作系统能够发现所有逻辑CPU核心。不同于物理核心,逻辑核心是基于超线程技术划分的,并且每个逻辑核心拥有独立的APIC。借助ACPI,Maestro得以稳定枚举核心,为后续的多核管理奠定基础。 传统的中断机制由可编程中断控制器(PIC)承担,然而PIC只支持单核处理器,这限制了现代多核CPU环境的中断处理性能。为此,Intel提出了高级可编程中断控制器(APIC),在每个CPU核心内部集成本地APIC,同时使用I/O APIC对外部中断进行管理。APIC不仅兼容PIC以保证向下兼容,还丰富了中断管理功能,支持多核间的中断传递(IPI),这对于多核协调及启动其他核心极为重要。

Maestro利用APIC实现多核中断管理,包含中断向量映射与本地APIC定时器设置。 在多核启动流程中,x86架构仅有主核心在系统启动时默认运行,其他核心处于休眠状态。启动其他核心需要通过发送特定IPI信号,分别为INIT和STARTUP。这些信号遵循严格的时间间隔要求,Linux内核中对此延时进行了优化以适配不同CPU速度。Maestro借鉴这一机制,实现对多核的顺序唤醒并切换至保护模式,使各核心进入正常运行态。在此过程中,APIC定时器的精确度成为关键,Maestro通过将APIC定时器与HPET(高精度事件定时器)比较、校准其频率,确保延迟计数的准确性,从而顺利完成核心启动等待与核心间协调。

并非所有处理器核心都是独立的物理单元,超线程技术将物理核心划分为两个或更多逻辑核心,这使得单个物理核心能够同时运行多线程任务,提升整体吞吐量。Hyper-Threading技术下,同一物理核心的逻辑核心共享L1和L2缓存,操作系统在调度时需尽可能避免频繁切换这些逻辑核心以减少缓存失效带来的性能损失。Maestro通过建立CPU拓扑树,具备从线程到物理核心再到处理器封装的多层次结构,辅助调度算法理解核心之间的关系,从而做出更符合硬件缓存层次的任务分配决策,提高缓存命中率及运算效率。 为了实现高效的任务调度,Maestro为每个核维护独立的调度器和运行队列。这些运行队列是双向循环链表结构,存储处于就绪状态的进程。调度器以时间片轮转方式选择下一运行进程,并在进程阻塞或退出时进行上下文切换。

核心定时器会定时发出中断,触发调度器重新分配CPU资源。与此同时,进程主动yield和等待外部资源等行为也会调用调度功能,确保CPU资源合理分配且响应灵活。 在多核环境中,负载均衡是保证系统稳定高效的关键。Maestro基于FreeBSD的ULE调度策略,综合考虑历史运行CPU负载、进程优先级及核心空闲状态,为新就绪进程选择最佳执行核。策略优先尝试重新绑定到先前运行进程的核心,以保持CPU缓存亲和性。如果失败,调度器会查找距离最近的空闲核心,然后选取负载最低的核心,实现整体负载均衡。

此外,内核设有后台平衡线程定期迁移进程,维护调度队列平衡,避免部分核心过载而其他核心空闲的不良状态。 虚拟内存管理中,翻译后备缓冲(TLB)是提升地址转换速度的关键缓存。不同核的TLB内容不自动同步,内存映射更改后必须通知所有相关CPU失效对应缓存,称为TLB shootdown。Maestro通过跟踪各内存空间绑定核心的位图,精准向相关核心发起无效通知,采用跨核延迟调用机制实现同步更新,保证虚拟内存一致性及系统稳定。 内核多核间通信关键技术是延迟调用,即在指定CPU核心上执行特定函数。Maestro为每核心搭建多生产者单消费者队列,源核将函数封装入目标核的队列并发出IPI通知。

此机制支持同步和异步调用,配合调度器即可实现跨核任务协同,极大提升系统整体效率与响应速度。 多核系统中临界区管理尤为重要。以往单核通过关闭中断避免抢占,但多核需允许中断同时禁止进程切换。Maestro引入多级计数器,支持嵌套临界区管理,内核中断处理程序通过标志位协调重调度请求。当进程退出最后一层临界区时,根据标志判断是否立即调度,保证安全性与性能。 然而,Maestro当前的多核机制仍有改进空间。

比如对遗留的PIT定时器支持近期放弃,仅依赖HPET导致缺乏兼容性;x2APIC尚未实现限制了对大规模多核支持;P核心与E核心未区分使用,影响异构处理性能;系统内存分配存在全局自旋锁瓶颈,影响并发;中断处理不支持核间绑定,限制了硬件中断性能优化;mutex设计实则简单自旋锁,等待时浪费CPU资源。未来通过引入RCU机制、完善异构核心调度、改进内存锁与中断划分策略,Maestro将进一步提升多核性能与稳定性。 综合来看,Maestro的SMP与调度设计充分体现了现代操作系统对硬件多核复杂性的适配。从底层APIC中断管理、定时器校准,到逻辑核心Affinity和负载平衡,再到跨核虚拟内存同步与异步调用,全方位确保各核心高效合作。英特尔超线程对调度策略的挑战也被巧妙纳入核心拓扑树与调度约束,实现更优缓存利用及进程分布。虽然仍有改善余地,但Maestro在这条技术路径上已经迈出了坚实的步伐,未来将推动更多软件成功移植并应用,推动操作系统技术的开源创新与生态发展。

了解并掌握这些底层机制,不仅有助于操作系统开发者设计更高效的内核,也使应用开发者能更好地理解多核环境下的性能表现,最终达成软硬件的深度融合与优化。 。