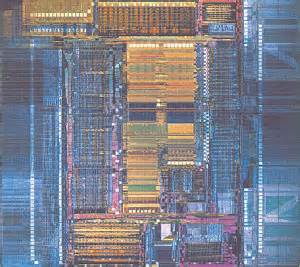

PA-RISC(Precision Architecture-RISC)是惠普(HP)在上世纪八十年代初期推出的一款基于精简指令集计算(RISC)理念设计的处理器架构。作为惠普技术理念的重要体现,PA-RISC不仅体现了当时计算机处理器设计的先进思潮,还在专业的Unix工作站和服务器市场中占据重要地位。经历了从32位到64位三个世代的演进,PA-RISC体现了RISC架构在计算性能和技术创新上的巨大潜力,成为与DEC Alpha并驾齐驱的第二大高性能RISC体系。本文结合PA-RISC的沿革及其竞争格局,深入探讨其架构性能和市场表现。惠普为了统一其16位堆栈型CPU和摩托罗拉CPU的系统架构,于1980年代启动PA-RISC项目,旨在打造一个基础扎实、设计简洁高效的计算平台。早期的PA-RISC处理器由HP的VLSI技术中心(VTC)及系统与VLSI技术部门(SVTO)主导,历经了从TTL和NMOS工艺线路到集成度更高的32位和64位产品。

PA-RISC 1.0时代(1986至1990年),代表机型如TS-1和NS系列,面临着MIPS R2000、SPARC、Intel i386等竞争对手。这一时期的PA-RISC在性能上保持与MIPS R3000及早期SPARC相当,但在时钟速度和浮点表现上略逊于IBM POWER1和Sun SuperSPARC。1990年代PA-RISC 1.1阶段则见证了PA-7000、PA-7100和PA-7200等CPU的推出,显现出明显进步,尤其是在浮点计算能力上大幅超越了同期Intel Pentium、MIPS R4000以及IBM PowerPC 604等微处理器。值得一提的是集成了内存和I/O控制器的PA-7100LC,它首创了将处理器核与外围控制器集于一芯片的设计,使HP的工作站产品线实现低成本、高性能的突破。进入1996年,惠普推出PA-RISC 2.0架构,使平台成功迈入64位时代,PA-8000处理器是这一转变的代表。PA-8000采用四向超标量设计和乱序执行技术,展示了出色的性能潜力。

该系列后续型号如PA-8200、PA-8500和PA-8600进一步提升了时钟频率和浮点处理能力,使PA-RISC在高端市场上能与Intel Pentium II、Sun UltraSPARC以及Digital Alpha系列处理器一较高下。尽管HP早期在芯片制造工艺上的进展相对缓慢,导致处理器频率提升受限,但随后与Intel合作采用其先进制造工艺,重塑了PA-RISC的产品竞争力。PA-8700作为PA-RISC最后一款传统单核设计,于2001年面市,旨在延续PA-RISC家族在Itanium处理器完全推出前的市场生命力。它结合改进的执行单元和更高时钟速度,成功维持与当时行业一线产品的竞争力。随着业界对多核架构的需求增长,惠普推出了集成双核的PA-8800及PA-8900,进一步挖掘PA-RISC架构潜力,这两个型号均利用了IBM生产的先进硅基绝缘体(SOI)工艺,确保了处理器在时钟速度和能效方面的稳定表现。虽然发布于二十一世纪初中期,但这些产品的设计理念和性能水准代表了PA-RISC家族的巅峰状态。

与此同时,惠普预见到了传统RISC技术的生命周期限制,开始与Intel合作研发基于显式并行指令计算(EPIC)理念的Itanium架构。Itanium处理器以其超长指令字(VLIW)设计推动了计算架构的新边界,但由于复杂的实现和市场竞争,未能完全替代PA-RISC。惠普在PA-RISC与Itanium之间的技术过渡,体现了行业巨头应对技术迭代的战略眼光。PA-RISC在性能基准测试中一直表现优异,尤其在浮点运算和科学计算负载中拥有明显优势。其SPEC(标准性能评测委员会)成绩显示,同频率下PA-RISC处理器常常超过同期IBM POWER系列和Sun SPARC处理器。得益于高效的指令流水线和大容量缓存设计,PA-RISC处理器成为专业技术领域热门选择,广泛应用于高性能技术计算、工程模拟及数据库处理等任务。

惠普通过持续的技术创新和产业链整合,使PA-RISC平台长期保持技术先进性和市场竞争力。尽管最终被Itanium架构所替代,但PA-RISC留下了深远的技术遗产,其设计理念和系统集成思路为后续处理器架构提供了宝贵经验。总的来看,PA-RISC架构代表了20世纪末期高端RISC架构的一个重要里程碑,其从保守的设计出发,经过不断优化,在性能和集成度上实现跨越式提升,充分印证了RISC思路在专业计算领域的生命力。随着计算技术的不断演进,PA-RISC的成功经验依然值得现代处理器设计者借鉴和启发。 。