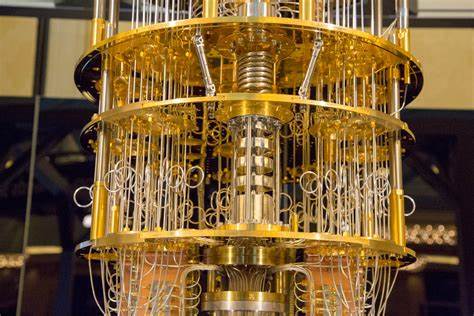

近年来,量子计算作为颠覆性技术,正不断吸引全球科技界的广泛关注。它有潜力解决传统计算机无法高效处理的难题,如复杂分子模拟、优化问题和密码分析等。作为量子计算领域的重要玩家之一,IBM近期公布了其首个错误容忍量子计算系统Starling的开发计划,标志着量子计算技术的一个里程碑式进展。这个系统不仅具备执行实用计算的能力,还能实现错误检测和纠正,预计2029年正式面市,将彻底改变人们对量子计算性能和稳定性的认知。传统量子计算机虽然展现出惊人的理论潜力,但其核心瓶颈之一是硬件错误率的限制。量子比特与环境相互作用极易引发噪声和错误,降低计算准确度。

IBM的Starling计划正是针对这一痛点,采用创新的错误纠正码和先进芯片设计,将设备的错误率降至超过百百万次运算无误的水平。量子错误纠正的关键在于如何利用多组硬件量子比特来代表和维护少数逻辑量子比特的信息。IBM选择的低密度奇偶校验码(LDPC)和具体应用的“双变量自行车码”算法,确保了逻辑量子比特的稳定存储和操作,同时兼顾纠错效率和硬件可行性。相比传统的“重六边形”芯片线路布局,IBM创新性地设计了多层互联电路,以实现量子比特之间空间上的远程连接。这种设计不仅突破了芯片制造的传统局限,还有效解决了线路串扰导致的错误问题,提升了整体系统的可编程性和可靠性。为了配合纠错算法,IBM推出了两款关键芯片“Loon”和“Nighthawk”,前者集成跨越多层布线的互联技术,后者则实现了紧凑的方阵量子比特排列,极大降低了错误率并提升了逻辑量子比特的密度和稳定性。

在2025年至2028年间,随着这些芯片的逐步发布和组合,量子系统的容错能力与逻辑运算规模将快速扩展。值得注意的是,IBM不再仅仅聚焦于单个物理量子比特的改进,而是转向构建功能完备的计算单元。通过将若干逻辑量子比特和辅助纠错量子比特整合为一体,再通过专门设计的“通用桥接器”将多个计算单元连接,IBM的量子计算体系架构体现了模块化和系统化的思路。这一设计理念不仅提升了系统扩展性,也为未来更庞大和复杂的量子计算机铺路。除了硬件创新,IBM还开发了面向经典计算机的实时纠错数据解码器。量子纠错产生的大量“综合症数据”需快速解析以反馈到量子系统中,才能维持低错误率。

IBM采用基于消息传递的解码算法,借助现场可编程门阵列(FPGA)的并行计算能力,实现了低延迟的错误纠正反馈。这一软硬件结合的全新纠错方案确保了Starling系统的高效稳定运行。未来的IBM量子产品路线清晰,由2026年发布的Kookaburra处理器起步,逐渐发展到2029年具备200逻辑量子比特的Starling系统,到2033年蓝鸦(Blue Jay)系统实现2000逻辑量子比特。每一步都围绕提高逻辑量子比特数及纠错能力展开,让量子计算逐步具备解决现实世界难题的能力。Starling系统的诞生不仅代表量子计算硬件迈入错误容忍阶段,也预示着从科研实验走向工程化落地的巨大飞跃。IBM高管普遍认为,量子计算中长期发展关键在于将科学难题转化为工程问题。

在这一框架下,Starling是回答科学疑问后的实际路径,集中于制造稳定、高效和可扩展的计算单元。这种转变为业界树立了重要示范效应。IBM的多层包装新工艺突破、方阵高连接性量子比特布局以及噪音抑制技术共同驱动了整体技术路径优化。应用方面,未来Starling及后续系统将在密码学、复杂材料设计、药物发现和优化算法等领域发挥深远影响。例如,量子计算具备潜在能力破解当前广泛使用的公钥加密体系,这带来网络安全的双重挑战与机遇。总体而言,IBM首次详细公布的错误容忍量子计算系统路线图,揭示了量子计算技术从理论证明走向实用部署的核心要义。

它将推动量子计算进入真实应用阶段,改变计算科学格局。同时,该系统代表了软件、硬件与系统架构协同创新的典范。随着IBM及全球各大科研机构持续努力,未来十年内量子计算必将造福更多领域,成为继经典计算后又一次巨大的技术革命。