在现代软件开发领域,性能优化始终是提升用户体验和系统竞争力的关键环节。特别是在处理复杂计算和数据密集型任务时,了解代码在硬件上的具体执行过程尤为重要。LLVM-mca作为一款基于LLVM项目的性能分析工具,通过模拟CPU执行机器码指令,帮助开发者深入洞察指令流水线、资源使用及瓶颈所在。它不仅能够揭示代码表面的执行效率,还能反映出背后的硬件交互细节,为性能调试提供了极富价值的参考。 LLVM-mca的核心优势在于其模拟能力,能够利用LLVM内置的调度模型,根据目标CPU的架构特性,静态分析机器指令序列的执行情况。不同于传统的性能分析工具侧重于运行时数据采集,LLVM-mca通过静态仿真评估指令的调度、资源冲突、延迟和吞吐量,帮助开发者预判代码在特定CPU上的表现,这尤其适合嵌入式开发和高性能计算场景。

为了具体展示LLVM-mca的实用性,我们可以以一个简单的一维卷积核代码为例,逐步剖析其性能调优过程。初始的C语言代码采用了双层循环,其中外层迭代输入数组,内层负责累加窗口区域内的乘积和。这种实现直观但在现代CPU中往往未能充分利用指令级并行和SIMD矢量化的潜力,限制了性能提升空间。 针对ARM NEON架构的优化思路通常是利用矢量化指令将多个数据元素并行处理。例如改写外层循环,让它每次迭代处理四个邻近的元素,同时用NEON指令加载、乘法和累加这些数据,以实现计算的并行化。经过一系列手工优化,最后确定使用vmlaq_laneq_f32等融合乘加指令,并在内层循环完全展开,减少了循环开销并提高了指令效率。

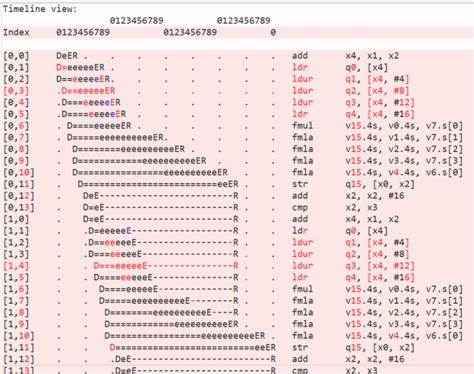

尽管从理论上减少内存加载次数能带来性能提升,但实际运行结果却显示优化后的版本反而变慢。为了排查这一反常现象,作者决定借助LLVM-mca的强大功能,将两段关键循环代码转换为汇编形式,通过模拟分别执行来对比资源利用和瓶颈情况。 LLVM-mca分析显示,虽然优化版本减少了加载指令数量,但新引入的vextq_f32寄存器延伸指令带来了额外的处理延迟。更为关键的是,优化代码中对执行资源的消耗更加集中,导致某些执行端口饱和,而原始代码则在硬件执行单元间的负载分布更加均衡。这种执行端口竞争引发的延迟,使得理论上的指令减少并未换来实际性能提升。 此外,LLVM-mca的时间线视图揭示了指令调度中的依赖链问题。

尤其是在累加计算过程中,连续的融合乘加指令无法并行开始,必须依次完成,形成实际执行的瓶颈。尽管加载寄存器的延迟有所不同,计算依赖关系依然限制了指令级并行度。 有经验的开发者建议引入多个累加器以打破长依赖链,从而提升指令吞吐率。通过将计算拆分成几个独立的累积变量,新的指令可以更早地被调度,减少流水线空闲时间,提高整体执行效率。这种方法在LLVM-mca仿真中可以明显看出收益,理论上使性能更加接近硬件峰值。 这次案例充分说明了LLVM-mca在性能分析中的独特价值,对于手写汇编优化、矢量化代码调优具有不可替代的辅助作用。

该工具不仅能够准确模拟程序在特定处理器上的执行周期,还能揭示执行端口分布、延迟来源和资源竞争等细节,使得开发者能够针对性地调整代码结构和指令调度,提高应用的性能水平。 当然,LLVM-mca并非万能,它模拟的是静态代码的回路执行,不涉及缓存层次、分支预测、内存带宽等动态运行时因素。因此,结合动态性能分析工具和实际性能测试结果,进行综合评估才是最佳实践。此外,针对不同的处理器架构,LLVM-mca的调度模型准确度有所差异,开发者要善于结合具体平台特性,灵活使用工具。 未来,随着计算复杂性不断增长和多核多线程的广泛应用,基于LLVM-mca的静态性能调试手段会变得更加重要。开发者通过深入理解指令执行细节,优化数据布局和指令顺序,能够最大限度挖掘硬件潜力。

与此同时,相关社区也在积极改进LLVM-mca,增加延迟判别、资源冲突细化和更精确的内存访问模型,为性能工程提供更为细致的辅助。 总的来说,LLVM-mca是连接源代码与CPU硬件之间的桥梁,帮助软件工程师准确定位性能瓶颈。无论是编写高效嵌入式代码、优化图像处理算法还是提升数据中心程序执行效率,熟练掌握LLVM-mca并结合矢量化优化策略,都是提升软件性能的重要路径。对性能调试充满热情的开发者,值得花时间深入研究这个工具,打磨自己的代码,从而在激烈的技术竞争中脱颖而出。