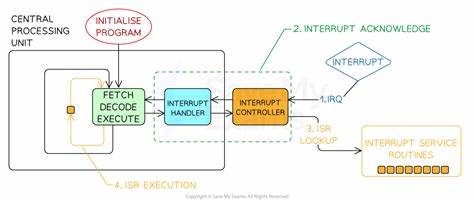

在现代计算机体系结构中,中断处理机制是实现系统灵活响应各种事件的关键环节。中断不仅能够让处理器及时响应外部或内部事件,还能够有效管理多任务操作,确保计算机系统的稳定性与高效性。深入理解微操作级别的中断处理,有助于更好地掌握计算机执行周期的细节,优化系统性能。本文将从微操作的角度出发,详细剖析中断处理流程的核心步骤以及相关技术细节,为架构设计和系统优化提供指导。首先,需要明确什么是微操作。微操作是计算机中最基础的控制命令,它在每个时钟周期内对寄存器、总线、存储器等硬件模块进行精确操作,是指令周期中更细粒度的操作。

在中断处理过程中,系统需要执行特定的微操作序列,以保存当前执行状态,切换程序计数器(PC)到中断服务程序(ISR)的入口地址,完成硬件状态的切换和更新。中断处理的微操作周期通常紧随指令执行周期之后。当正常指令执行完毕后,系统会测试是否有待处理中断请求。如果存在有效且优先级较高的中断,系统就会进入中断处理周期。以常见的中断微操作流程为例,首先需要将当前程序计数器PC的内容保存到某个安全的存储位置,以防止中断服务程序执行完毕后回到中断前的正确执行地址。这一步一般由将PC的值加载进内存数据缓冲器(MBR)完成,准备将其写入指定内存地址。

接下来,系统将要保存PC值的存储器地址装入存储器地址寄存器(MAR),与此同时将程序计数器重新加载成中断服务程序对应的起始地址,准备跳转到ISR开始执行。然后最后一步,将MBR中的程序计数器值存入指定内存单元,实现现场保存。值得注意的是,具体的微操作序列和寄存器使用方式会因计算机体系结构的不同而有所差异,这是为什么不同教科书或资料中给出的微操作指令看似不同的原因。某些体系结构可能还涉及栈指针操作、中断向量检查或优先级判断等附加操作。理解微操作层面的中断处理,有助于深入把握计算机流水线的设计思想以及指令周期内各阶段的细节。中断处理不仅要完成上下文保存和恢复,还要保障数据的一致性和指令的顺序执行,这对于高性能处理器的设计尤为关键。

同时,微操作层级的中断管理也为处理器设计提供了丰富的调优空间。例如,可以通过优化中断响应时间减少系统延迟,改进寄存器传输路径提高功耗效率,或者设计多级中断优先级机制增强系统的实时性。除了硬件实现层面,中断的微操作管理对于操作系统的中断服务程序设计同样重要。操作系统需要依赖底层的中断微操作机制,实现多任务调度、中断屏蔽和嵌套处理,从而保障系统的整体安全和稳定。理论上,中断微操作的核心总是围绕保存现场、加载新程序计数器地址、进入中断服务程序执行,并在中断服务完成后恢复现场,实现流程的有序切换。综上所述,中断处理在微操作级别的实现,是现代计算机体系结构设计的基础且不可或缺的部分。

通过理解和掌握这些细微操作,可以更好地进行计算机系统分析、设计与优化。无论是硬件工程师还是系统软件开发人员,熟悉中断微操作机制都能提升解决复杂问题的能力,推动计算机技术的发展。未来随着计算能力提升和体系结构多样化,中断处理的微操作设计也将呈现出更多创新和优化的可能性,为高效、智能的计算环境添砖加瓦。 。