在人工智能快速发展的今天,深度神经网络(DNN)已成为实现复杂任务的核心工具。然而,传统的DNN训练与推理过程中存在许多瓶颈,尤其是在资源受限的硬件环境中,如何保证模型的高效运行同时支持持续学习与少样本学习成为亟需解决的重要问题。来自荷兰代尔夫特理工大学认知系统实验室团队推出的一款名为Chameleon的开源DNN加速器,为这一领域注入了新鲜活力。 Chameleon是一款针对时序数据设计的无矩阵乘法时序卷积网络(TCN)加速芯片,它独特地集成了少样本学习(Few-Shot Learning, FSL)和持续学习(Continual Learning, CL)功能。该芯片不仅实现了所有权重全片上存储,避免了依赖外部嵌入器的瓶颈,同时还在逻辑面积和功耗方面做到了极致优化。设计者通过对原型网络(Prototypical Networks)的重新构建,将少样本与持续学习嵌入推理流程,极大地简化了硬件复杂性,且耗时和能耗均几乎可以忽略不计。

在精度性能方面,Chameleon尤其突出。在官方测试中,该加速器成功实现了250类手写字符的持续学习示范,准确率甚至超越了此前仅支持少样本学习的先进方案。此外,采用TCN作为时序数据的嵌入器,使得该芯片在处理关键词识别等任务时表现优异。在谷歌语音指令数据集上的实验结果显示,Chameleon能够在3.1微瓦的实时功耗下达到93.3%的准确率,远超传统的推理加速器表现。 Chameleon的设计理念灵活且高度可配置。无论是想运行小型片上时序卷积网络,还是搭建较大规模的网络,芯片均能通过可重构的处理单元阵列适应不同需求。

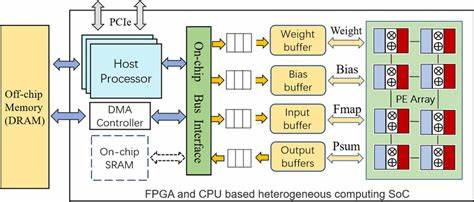

开发者可以根据应用场景,选择优化运行吞吐量或者降低静态功耗,满足从嵌入式设备到高性能计算需求的广泛应用。 该项目开源时,团队配备了完善的软件工具链支持从PyTorch训练到硬件部署的全流程。用户可以先利用任意深度学习框架训练TCN模型,随后应用提供的量化感知训练工具包进行权重量化,最后导出模型并通过Python接口在芯片或FPGA上进行仿真及实际运行。针对FPGA桥接代码,开源项目同样给予了极大便利,方便研究者与工程师快速进行原型验证和二次开发。 目前,Chameleon的硬件描述语言(HDL)代码采用最新Verilog编写,并通过Bender工具实现依赖管理及代码生成,保证了设计的模块化与灵活性。测试方面,该项目基于cocotb框架构建了全面的单元与系统级测试,确保了高可靠性。

与此同时,项目文档虽然尚处于持续完善中,但用户社区鼓励反馈和问题提交,彰显了开源项目的开放精神和协作氛围。 与传统DNN加速器相比,Chameleon的最大亮点之一是其避免了大量的矩阵乘法运算,而是利用时序卷积网络高效处理序列数据。矩阵乘法一直是神经网络推理速度和功耗的主要瓶颈,绕开这一环节不仅降低了逻辑和动态功率消耗,也使得硬件实现更加轻量与高效。对于需要处理长序列如16kHz原始音频数据的应用,Chameleon实现了业内首次全片上端到端处理,不需外部预处理或嵌入,极大简化了系统设计。 少样本学习和持续学习作为机器学习的重要热点,一直以来都难以在边缘设备或专用芯片上高效实现。多数方案通常依赖云计算或大容量存储,极大限制了实际落地场景。

Chameleon通过将这两种学习能力融入硬件本身,不仅提升了推理速度,也赋予设备自适应能力,让机器能够在使用过程中不断学习和适应新数据,开创了新的智能硬件范式。 从生态建设的角度看,Chameleon项目也表现出色。除了硬件和驱动代码外,团队配套开发了基于NumPy的仿真环境,方便开发人员在硬件部署前验证模型准确率和性能表现。项目还提倡学术和商业用户在使用时反馈体验,助力持续优化与发展。此外,硬件代码采用Solderpad硬件许可证,软件部分采用Apache 2.0协议,确保了开源、安全且灵活的商业友好性。 未来,Chameleon的设计理念和架构能够为语音识别、传感数据分析、生物信号处理以及多模态序列数据的边缘AI应用提供强大支持。

这种赋予硬件智能进化能力的加速器,也将激发更多行业探索终端智能、新型交互及个性化服务的创新。 综合来看,Chameleon项目以最前沿的算法及硬件协同设计,将深度学习中最为棘手的少样本与持续学习问题巧妙地落地于芯片中,展现出DNN加速器未来的发展方向。对于研究者和工程师而言,Chameleon不仅是一件功能强大的工具,更是一笔宝贵的开源财富,助力人工智能技术向更高效、更智能、更广泛的应用迈进。随着开源社区的不断壮大和优化积累,期待这款革命性加速器在更多实际场景中创造价值,推动AI硬件生态进一步繁荣。