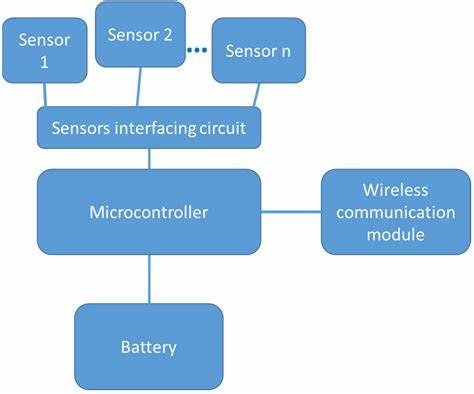

随着人工智能技术的飞速进步,越来越多的智能应用开始迁移到边缘设备,尤其是资源有限的微控制器上。微控制器作为嵌入式系统的核心硬件,因其低功耗、小尺寸以及成本优势,被广泛应用于智能传感器、可穿戴设备以及家居自动化等领域。然而,如何在微控制器这种计算和存储资源都十分有限的环境中高效运行复杂的AI模型,成为了业界关注的热点。而计算图作为连接AI模型与底层硬件执行的桥梁,发挥着至关重要的作用。理解计算图的原理,不仅有助于开发者更好地利用微控制器资源,还能显著提升AI推理的性能。计算图本质上是一种将AI模型中各个运算节点和数据流动关系以图结构形式表示的机制。

每个节点代表一个操作符,比如卷积、池化或激活函数,而边则表示节点间数据的传递。通过对计算图的解析和调度,推理引擎能够按照正确顺序执行模型中的算子,确保数据准确流转并生成结果。在微控制器上运行AI模型时,计算图不仅决定了执行流程,还影响内存分配和运算效率。以TensorFlow Lite Micro(tflite-micro)为例,其使用的.tflite文件格式即包含计算图信息。该格式基于FlatBuffers编码,它能够紧凑高效地存储模型的所有细节,包括算子类型、连接关系和权重数据。这种封装方式使得一个模型文件就能包含完整的推理所需信息,简化了部署流程。

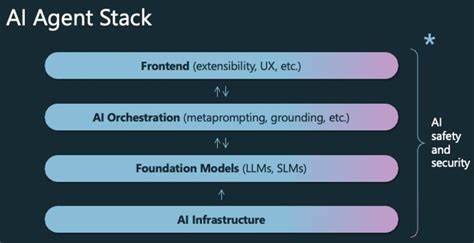

与此不同的是,一些格式如PyTorch的pickle文件或GGUF格式,往往不包含计算图,而是需要额外代码支持推理逻辑,这在微控制器环境中带来了实现复杂度和资源消耗的增加。计算图中每个算子对应的实现称为内核(Kernel),它是操作具体执行的代码。内核可以针对不同硬件进行优化,比如基于指令集架构(ISA)的运算加速。当微控制器配备了神经网络加速器(NPU)时,模型中的算子可被编译成NPU支持的内核,从而显著提升推理速度并降低能耗。例如,Arm的Ethos-U NPU通过将复杂的算子序列打包为一个自定义算子(ETHOSU),让微控制器核心CPU只需简单触发神经加速器执行,极大地减轻了CPU负担。文章中提及的MobileNetV1模型示例显示,通过tflite-micro框架注册所需的基础算子(卷积、池化、Softmax等),并结合计算图信息,推理引擎能够顺序执行算子,实现人脸检测等功能。

此处模型文件转换成C数组以适应无文件系统的固件环境,同时保证了存储效率。对比之下,基于ggml的YOLOv3-tiny实现则需在运行时动态构建计算图,明确每个节点的输入输出关系及所用权重,对理解计算图构造流程提供了直观示范。计算图还为模型优化提供可能。编译器和优化工具根据计算图结构对算子执行顺序、内存占用以及并行化潜力进行规划,助力减小模型尺寸并提升运行效率。尤其是在微控制器这样有限资源的环境中,高效的计算图设计和调度能够显著节省宝贵的存储空间和计算时间。此外,计算图的可移植性使得相同模型能够在多种硬件平台间灵活迁移,只需针对目标设备支持的算子注册对应内核即可。

通过采用标准化格式(如.tflite或ONNX)存储计算图,开发者可以无缝切换运行时和硬件,实现AI推理的广泛兼容与扩展。不可忽视的是,计算图的设计也促进了模型的可解释性和调试便利。开发者可根据计算图结构轻松追踪数据流路径,定位性能瓶颈或计算错误,快速迭代模型和代码。结合调试工具输出的张量形状和数值信息,可以有效提升模型开发效率。总结来看,计算图是微控制器上AI推理的核心枢纽。它不仅承载了模型运算流程的完整信息,还指导了内核调度和资源管理。

通过规范的模型文件格式承载计算图,推理框架能够实现跨平台兼容、简化部署流程,同时支持针对特定硬件优化内核执行,提高速度与能效。展望未来,随着微控制器性能提升以及神经加速器的普及,计算图与模型编译技术将更加紧密结合,推动边缘AI应用不断向更高效、更智能方向发展,赋能更多创新场景和应用领域。