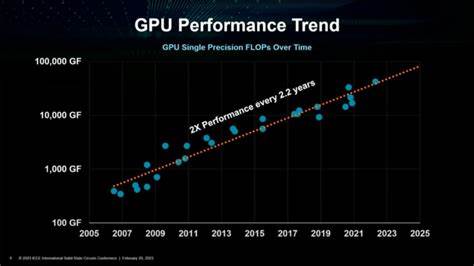

随着计算机图形学和并行计算需求的不断增长,GPU的重要性愈发凸显。现代GPU内部包含了大量SIMD单元,其核心任务是读取数据、执行向量或标量算术逻辑单元操作(分别简称VALU和SALU),并将结果写回渲染目标或缓存缓冲区。这些单元通常被封装在NVIDIA所称的流式多处理器(Streaming Multiprocessors,SM)或AMD称之为工作组处理器(Workgroup Processors,WGP)中。保持这些SIMD单元的高效利用率和VALU吞吐量对于提升渲染任务的性能尤为重要,特别是在当今GPU单元规模持续扩大、计算能力不断增强的时代。 在数据传输方面,SIMD单元依赖于一系列固定功能单元,诸如纹理单元(TEX)负责处理纹理数据请求,寄存器文件用于存储临时数据(VGPRs),光栅操作单元(ROP)完成渲染目标的写入,此外还有多级缓存系统加速数据的读取与存储。虽然这些固定功能单元设计简洁且响应速度快,但仍可能成为限制SIMD单元高效运行的瓶颈,进而导致计算单元处于等待状态,无法充分利用其运算能力。

因此,图形程序员的核心工作之一是对渲染工作负载进行详细分析,识别并消除由固定功能单元(如输入装配器(IA)、光栅化单元、内存带宽等)引起的瓶颈问题。譬如,阴影贴图渲染过程通常对VALU计算需求较低,而更多受限于顶点数据传输和世界空间流水线(World Pipe)相关的输入处理,导致SM的执行吞吐率较低。又如某些计算着色器用于复制渲染目标或构造深度Mip链时,着色器的计算负载很轻,无法充分驱动SIMD单元,这些场合的性能优化应放眼整帧渲染任务,寻找整体提升空间,而非单一调用。 锁定并解除瓶颈的第一步是准确识别阻碍性能的关键资源。各种GPU分析工具,包括NVIDIA Nsight Graphics的GPU Trace、AMD Radeon Profiler及微软的PIX,提供了资源利用率和吞吐率的实时数据视觉呈现。通过这些工具,可以直观观测例如阴影贴图阶段主要瓶颈集中在显存带宽与顶点输入,而全局光照近似(GTAO)则受限于L2缓存,光线追踪影子遮罩计算依赖RT单元。

明确瓶颈所在,能够帮助开发者将精力集中在优化最关键部分。 优化策略首先着眼于提升单个高成本绘制调用的VALU利用率。若瓶颈表现为内存延迟 - - 即GPU计算指令需等待数据抵达,开发者可优化向量寄存器分配(VGPR)减少寄存器占用,重新设计着色器代码结构以增加内存请求与数据使用间的指令间隔,例如部分循环展开,也是常用技巧。此外,提高数据流通效率,比如压缩或打包着色器输入输出数据,优化数据访问模式,选择适宜的数据结构(例如在NVIDIA GPU上,结构化缓冲区对随机访问表现更优于常量缓冲区)都有很大帮助。 当有效优化单一任务变得困难时,调整着色器的占用率成为新的突破点。过高的占用率可能引发缓存争用,导致不同执行波同时访问缓存而带来抖动。

此时,适当降低线程组内活跃波的数量,诸如增加VGPR分配(例如编写条件永不成立的大型动态分支)或在计算着色器中分配组共享内存(LDS)成为实现控制的手段。相比静态分配寄存器,LDS分配更具优势,它不仅限制了占用率,还有助于释放资源给并行运行的其他任务。提升VGPR分配亦有可能让编译器在着色器起始批量加载纹理,进而降低内存访问延迟。 针对具体任务选择适合的着色器类型同样关键。像素着色器处于GPU几何处理管线末端,数据输入依赖光栅化单元及顶点着色器导出,输出受限于ROP单元,这使得某些情况下像素着色器成为瓶颈。此时,将部分工作移植至计算着色器可规避这些固定功能单元依赖,因计算着色器可利用组共享内存实现线程间数据交互,大幅提升执行效率。

然而,像素着色器在某些GPU架构中具备专用的"颜色缓存"等硬件优势,能够直接与显存交互,绕过二级缓存,进而优化渲染目标写入性能。此外,像素着色器支持硬件可变速率采样(VRS)、深度和模板测试,这些优化在计算着色器中实现难度更大,需权衡利弊。 工作线程的分布模式也影响性能表现。计算着色器通常将整个线程组调度到同一SM或WGP执行,有助于缓存一致性和数据局部性,对于需要高效共享数据的大线程组尤为适合。但大线程组资源占用较多,例如VGPR和LDS需求较高,可能导致调度延迟。相比之下,像素着色器的执行波以屏幕瓦片为单位更规律地分布,利于整体执行的可预测性和效率。

部分情况下,将计算负载转移到顶点着色器也许会缓解像素着色器压力,但这种策略风险较大,因顶点着色器的波启动模式可能破坏缓存一致性,并且为剔除的三角形浪费计算资源,也可能加重顶点到像素数据传递瓶颈。 在GPU架构层面,不同硬件对波大小的支持和默认设置也会影响性能。例如RDNA架构上,计算着色器默认使用32线程(wave32)执行,而像素着色器为64线程(wave64)。因64线程的波可以同时处理更多线程间数据共享指令(wave intrinsics),依赖这类指令的着色器在像素着色器阶段可能获得更高性能。反之,存在较多分支发散的着色器在32线程基础上可能更快完成执行。值得关注的是,自SM6.6以后,HLSL规范引入了对计算着色器波大小的配置支持,允许针对具体硬件环境调整线程组大小,进而调优性能。

将一些适合的工作负载转移到计算着色器带来额外优势,即支持异步计算的并行执行。这意味着计算着色器任务可以在图形流水线如顶点和像素着色器正在运行时,异步利用GPU资源执行,提升整体VALU利用率。通过这种方式,可以巧妙地将不同时段或不同瓶颈的任务协同运行,例如一个缓存和SM瓶颈限制的全局光照近似任务可与一个受光线追踪核心限制的阴影遮罩渲染任务并行运行,实现资源最大化利用。类似地,轻负载的深度预通道或阴影通道任务也能与计算着色器任务交叠执行,增强吞吐率。 需要注意的是,目前主流图形API并未广泛暴露异步计算任务的优先级或调度策略接口,且不同硬件对调度的响应各异,这或导致异步计算对图形流水线的潜在负面干扰。优化异步任务时,通过调整线程组大小、分配虚拟寄存器和组共享内存资源,能够间接影响调度行为。

通常较小的线程组更容易与图形流水线任务良好重叠,但具体配置需在真实项目中多次试验验证,以获得最佳效果。同时,部分GPU架构允许计算任务内通过无障碍执行(barrier-free)策略,实现计算、顶点、像素着色器的更加灵活并行。 在提升GPU性能的道路上,消除固定功能单元以及其他资源瓶颈,实现SIMD单元的高效计算利用,是必不可少的技术环节。无论是单个绘制调用或分派任务的精细优化,还是利用异步计算实现任务并行,开发者都拥有多样化工具和方法可供选择。然而,鉴于GPU架构种类和设计理念的多样性,通用的优化方案难以一概而论。每款硬件的核心瓶颈与调度机制不同,实际调优需要结合具体应用场景、着色器复杂度和硬件环境,经过反复性能分析和验证得出。

对于欲提升GPU利用率及整体性能的开发者来说,持续进行深度分析和针对性调优,是实现显著性能提升的关键。通过合理安排数据流通、优化寄存器使用、选择合适的着色器类型、利用异步计算并巧妙调整线程组结构,均有望破解性能瓶颈,释放GPU潜能。在未来GPU架构不断演进和计算需求不断攀升的趋势下,灵活掌握和应用上述技术,将成为打造高性能、低延迟图形渲染与计算应用的重要利器。 。