近年来,随着开源硬件设计理念的兴起,FPGA(现场可编程门阵列)领域发生了深刻的变化。传统FPGA设计依赖于大型供应商提供的专有工具,这不仅限制了设计者的自由,也增加了研发成本和时间。开源合成工具的出现,极大地降低了设计门槛,促进了创新生态的形成。在这场变革的浪潮中,Zero ASIC作为新兴企业,凭借其一系列开源FPGA合成工具和创新芯片解决方案成为行业焦点。Zero ASIC致力于"民主化硅片设计",强调以开源软件和硬件推动整个半导体行业的透明度与开放性。它们推出的Wildebeest合成工具,以其开源特性和卓越性能,首次达到了与传统专有合成工具媲美的质量水平。

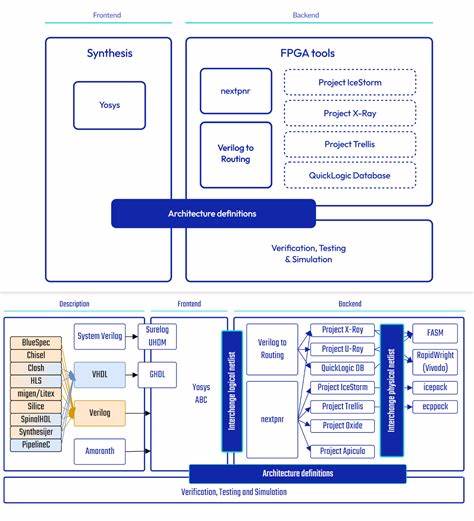

Wildebeest不仅提供了高效的逻辑合成功能,还支持复杂设计的静态时序分析,使得多时钟域设计的分析变得更为便捷和精准。这对于FPGA设计者大大提升了设计验证的速度和准确度。除了Wildebeest之外,Zero ASIC还发布了Platypus异构嵌入式FPGA(eFPGA)核心系列,以及Logik开源FPGA综合与比特流生成工具链。Platypus打破了FPGA长久以来面临的供应商锁定问题,使设计者能够灵活嵌入可重新配置逻辑模块。Logik工具链则以Python驱动的自动化流程著称,支持从RTL(寄存器传输级)到比特流的一键式设计体验,极大简化了FPGA开发周期。Zero ASIC的大量项目和产品都建立在SiliconCompiler这样的开源硅片编译平台基础之上,体现了从软件到硬件完整生态链的开源哲学。

SiliconCompiler为FPGA设计提供了模块化、可扩展的工具接口,允许设计者根据需求自定义并灵活集成不同的工具和IP核。开源静态时序分析工具的推广也成为亮点。FPGA设计中的时序闭合一直是挑战难点,传统一体化的专有工具往往价格昂贵且闭源,限制了设计调试和优化的深度。由Zero ASIC等组织推动的开源静态时序分析流程,让设计师得以深入理解时序瓶颈,进行精准优化,提升设计性能。除此之外,社区力量的壮大促使多种开源工具和IP核不断涌现,为FPGA设计带来丰富资源。例如,Mask ROM、可编程内存、数字信号处理(DSP)模块等都已有高质量开源实现,设计者可以自由组合,构建符合自身需求的定制化硬件。

全球多家顶尖大学和研究机构也积极投身于FPGA开源工具生态的打造,提供学术支持和实际案例,推动产业界和学界密切合作,形成创新驱动的良性循环。全球芯片设计中心的部分重要趋势之一是芯片let技术的出现。Zero ASIC预计,通过将FPGA集成到芯片let生态,设计者可以实现更高的硬件组合灵活性和更强的系统级优化能力。这种方式极大提升了芯片再利用性,降低了设计复杂度和制造成本。零ASIC的首席执行官Andreas Olofsson多次强调,未来FPGA设计的突破将不再局限于单一层面的硬件改进,而是要实现软硬件协同的"机械可重构"设计理念。通过动态硬件配置和软件化芯片架构,设计团队能够实时调整硬件资源,极大提升了应用适应性和性能表现。

FPGA开源生态的成长不仅带来了技术红利,也对国家层面的半导体安全和供应链产生了积极影响。开源工具减少对特定供应商依赖,增强了技术自主权,符合如美国政府等对本土芯片制造和设计能力提升的战略需求。展望未来,开源FPGA合成工具有望在性能、易用性和生态兼容性上持续突破。随着人工智能、物联网和5G等领域对定制硬件需求激增,开源工具将为中小企业和独立开发者开辟新的创新天地。整体来看,开源合成工具正重塑FPGA设计的行业格局。借助Zero ASIC等先锋企业的技术积累和活跃社区的支持,设计者正迎来一个更加开放、灵活且高效的硬件设计新时代。

只要持续关注这一领域的最新动态,积极参与到开源项目中,未来的硬件创新与价值创造将不再被大型供应商垄断,而是由全球设计者共同推动,实现真正的芯片民主化。 。