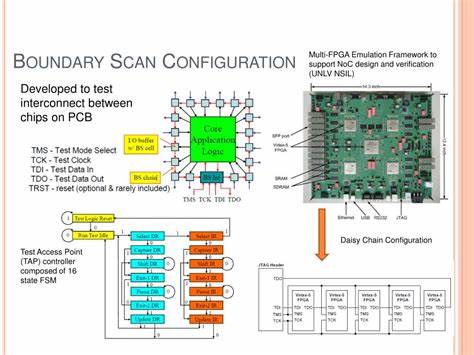

在现代电子板级测试中,边界扫描(Boundary Scan)已经成为 FPGA 器件制造验证与产线测试的重要利器。随着 AMD 并购 Xilinx 后其 FPGA 家族(包括 Spartan、Artix、Zynq、UltraScale+、Kria 系列等)在嵌入式与加速应用中广泛使用,如何有效利用 JTAG/TAP 与边界扫描能力来提高故障覆盖率、缩短调试周期和降低产线成本,成为工程师必须掌握的技能。本文从原理、工具、实践与注意事项等多角度展开,帮助你把边界扫描融入 FPGA 板卡从开发到生产的整个流程。 边界扫描基于 IEEE 1149.1 标准,在 FPGA 的每个 IO 引脚附近内建测试单元,这些单元可以在测试模式下将 IO 信号串入一个称为数据寄存器(Data Register, DR)或边界寄存器的移位链,通过 JTAG 的测试访问端口(Test Access Port, TAP)和四线信号(TCK、TMS、TDI、TDO)进行串行控制与观测。标准还定义了多种测试指令,常用的有 EXTEST(外部测试,用于驱动或采样边界引脚以验证器件间连通性)和 SAMPLE/PRELOAD(采样/预载,用于在不干扰正常设计运行的情况下采样 IO 或把期望值预载到边界寄存器)。通过这些机制,工程师可以在不必运行内部设计逻辑的前提下检测焊接缺陷、短路、开路以及接口连线问题。

对 AMD/Xilinx FPGA 而言,边界扫描的能力是由器件的边界扫描描述文件(Boundary Scan Description Language,BSDL)来描述的。BSDL 文件采用类似 VHDL 的语法,定义了器件的边界寄存器结构、引脚映射以及哪些引脚支持哪些边界扫描功能。通常有两类 BSDL 文件会被使用:厂商提供的"未编程"BSDL,它描述了原始器件的边界扫描能力;以及由综合并实现后的 FPGA 生成的"已编程"BSDL。后者可以通过 Vivado 的 write_bsdl 命令导出,反映了最终设计中 IO 单元的配置和映射,从而支持 SAMPLE/PRELOAD 等在已实现设计下更精确的测试。 在实际工程中,使用已编程 BSDL 带来两个显著好处。其一,它允许在保留设计功能的同时进行间接观测和控制,例如对特定信号做 SAMPLE 而不影响逻辑功能;其二,它能在测试向量生成时更准确地映射实际管脚电气属性,提升异常检测的准确率。

生成已编程 BSDL 的典型流程是在 Vivado 中完成实现(implementation)步骤后,在 Tcl 控制台运行 write_bsdl 命令,导出适配当前 bitstream 及 IO 配置的 BSDL 文件,然后把该 BSDL 导入到边界扫描测试工具(例如 XJTAG、Goepel/JTAG Technologies、JTAGLive 等)中进行向量生成与仿真。 边界扫描在多器件链测试中表现尤为突出。在板卡上如果有多个 FPGA、微控制器或其他支持 JTAG 的器件,可以把它们串联成一条 TAP 链,一次性对整条链路进行访问与检测。这样能在产线上对多个器件之间的连线、时钟分配网、复位网络以及外围器件的连通性做快速检查。针对此类应用,需要在设计阶段就规划好 TAP 的物理连线、测试点和 JTAG 接口的可访问性,避免在模块封装或外壳装配后无法接触到 JTAG 接口而影响测试。 边界扫描不仅用于连线检测,也能用于对外部存储器(包括 SDRAM、NOR、NAND、FRAM 等)的简单功能测试。

通过把 FPGA 的地址线、数据线和控制线置于边界扫描控制下,可以对存储器做地址/数据交替写入、读取并比对,从而检测焊接缺陷、短路或线路错误。需要注意的是,边界扫描通常无法直接访问器件内部的片上 RAM 内容,除非设计中包含特殊的扫描或内建自测逻辑。因此针对复杂的内存一致性或性能测试,仍需结合 FPGA 内部逻辑、VIO/ILA 或系统级测试工具。 在工具与设备方面,市面上存在多种边界扫描硬件与软件解决方案。面向实验室和小批量开发的有如 JTAG Live pod、Xilinx Platform Cable USB 等,而用于量产的专业方案包括 XJTAG、Goepel ScanWorks、JTAG Technologies 等,它们通常提供更完善的向量生成、测试脚本、自动化接口以及与 AOI/ATE 的集成能力。开源工具如 UrJTAG 或 OpenOCD 在某些场景下可提供基本 JTAG 访问,但在边界扫描向量生成、BSDL 导入和复杂测试脚本支持方面通常不及商业工具。

选择何种工具需要根据项目规模、预算、测试覆盖率目标与自动化需求来平衡。 要把边界扫描有效地引入项目,有一系列工程与生产上的实务建议值得遵循。首先,在方案选型与原理图设计阶段就要为 JTAG 留出合理的接口,包括清晰标注的 JTAG 插针、必要的上拉/下拉阻值和避免在 TCK、TMS 等线上放置会影响信号完整性的缓冲器或隔离器。对于跨电平的 JTAG 链,建议使用专门的多电压 JTAG 适配器或设计可控的电平转换策略,避免在链中出现无法访问的节点。 其次,在 PCB 组装时要考虑 JTAG 可达性与夹具设计,产线夹具通常需要方便快速接插件或夹具接触 JTAG 点。若设计中包含多个可选器件或可拆卸模块,提前规划 TAP chain 的可重配置能力能够极大提升测试灵活性。

例如在开发阶段把模块 TAP 串联,而在量产阶段通过跳线或焊盘改变链路顺序以优化测试步骤。 再次,BSDL 与测试向量的管理同样关键。建议把厂商未编程的 BSDL 作为基线文档保存,同时在每次实现后用 Vivado 导出已编程 BSDL 并与版本控制系统一起管理。测试向量应基于已编程 BSDL 生成并在每次板卡版本更新、PCB 修改或器件替换后重新验证。通过将 BSDL、测试向量与生产工艺参数挂钩,可以在问题追踪时迅速定位是设计变更引入的问题还是装配缺陷。 在编写测试策略时,边界扫描测试往往与功能测试、接口协议自检以及系统级自诊断相结合以提高覆盖率。

边界扫描在检测短路与开路方面效率极高,然而对某些类型的故障(例如间歇性接触、微小阻抗不匹配、由于封装内部损伤导致的内部寄生故障)则可能无法完全覆盖。为此,可把边界扫描作为首级快速筛查手段,对通过或失败的板卡再分配给更精细的故障隔离流程,如示波器探测、EMI 测试或 ATE 更高级的测试。 在实际项目中的典型工作流可以这样组织:先在设计早期确认 JTAG 和边界扫描的需求,确保原理图与 PCB 为 TAP 链和测试器件留出接口;在实现阶段生成已编程的 BSDL,并用边界扫描工具对原理图生成测试向量;在样机评审和调试阶段通过 EXTEST 与 SAMPLE/PRELOAD 验证关键接口与外设连通性;在试产和量产阶段把边界扫描集成到 ICT/ATE 测试序列中,实现板卡的一键测试与判定。在此过程中,团队应对 BSDL 的变化、器件替换与 PCB 版本保持高度关注,及时更新测试向量以保证产线测试的稳定性。 边界扫描虽然功能强大,但也有常见的坑需要规避。最常见的问题是链路中某个器件进入不正确的 JTAG 状态或被配置为不响应 TAP,从而导致整个链停止工作。

出现这种情况时需要逐段隔离链路、检查上电顺序、复位网络以及是否有外部电平转换器影响 TDI/TDO 等信号。此外,某些 I/O 经过缓冲器、开漏结构或复杂的外部电路时,边界扫描驱动能力与采样响应会被限制,测试工具在生成向量时可能需要对这些引脚进行特殊处理或标注为不可测试。 最后,结合具体产品如 Kria K26 SOM、Spartan-7 开发板或基于 RPI2040 的混合系统,边界扫描可以显著缩短板卡 Bring-up 时间。在一个多模块系统里,通过边界扫描快速确定哪一段总线或哪一个模块连接异常,可以把调试焦点从整体缩小到局部,从而大幅提升工程师工作效率。对量产团队而言,边界扫描能把早期的返修率降低,并为持续的产品质量控制提供可量化的测试覆盖率数据。 综上所述,边界扫描在 AMD/前Xilinx FPGA 生态中是一项提高测试效率和可靠性的关键技术。

通过合理规划 JTAG 硬件接口、生成并管理已编程 BSDL、选择合适的边界扫描工具并将其与产线测试流程深度集成,团队能在开发、验证与量产各阶段获得显著收益。尽管边界扫描并不能替代所有类型的测试,但作为一种无侵入、可自动化的测试手段,它在今天复杂板卡设计与高产量制造场景中依然具有不可替代的价值。 。