随着计算机技术的迅猛发展,内存管理机制成为操作系统设计的重要基础,特别是在x86架构处理器中,翻译后援缓冲(TLB)和页表遍历一致性机制的设计直接影响着系统的性能与稳定性。自386处理器以来,x86架构便引入分页机制,通过多级页表将虚拟地址映射到物理地址,为应用程序提供连续的虚拟空间同时实现进程间隔离。页表数据存储于主存,而TLB作为高速缓存,极大提升了虚拟地址到物理地址转换的效率,避免每次访问都进行多级内存查找。然而,围绕TLB与页表的一致性问题却一直是体系结构设计中的挑战。 传统上,x86架构规范明确指出TLB并不自动与页表的主存状态保持一致,也不保证内存操作的顺序性。这要求软件层必须在页表修改后,显式发送无效化指令(如INVLPG或MOV CR3),以清除相关TLB条目或整个TLB,从而避免处理器使用过时的映射导致访问错误或系统崩溃。

这种非一致性设计,虽降低了硬件设计的复杂度和功耗,但使得操作系统的内存管理必须小心周全,特别是在多任务和多处理器环境中。 有趣的是,尽管规范未强制要求,一些真实的处理器实现却提供了更多级别的一致性保障,尤其是关于页表遍历过程中的一致性行为。当TLB无法命中时,处理器需发起页表遍历来完成地址转换。此时若页表刚经历修改,页表遍历过程中能否正确看到最新页表内容成为关键问题。Intel 和AMD的官方文档均指出,如果未执行TLB无效化,页表遍历可能会读取到旧的页表项,因此存在非确定性行为。 然而,操作系统中存在部分软件代码依赖这种“页表遍历一致性”的假设,尤其Windows 95至Me期间的内核代码,不经TLB无效化而直接修改页表。

这反映出实际处理器中某种更强页表遍历一致性机制的存在。针对这一矛盾,研究者通过微基准测试对多款x86处理器进行了细致测量,发现了三种主要页表遍历行为模式:完全非一致、非推测性一致以及推测性一致。非一致型处理器的页表遍历在未获无效化时直接可能读取旧页表项;非推测性一致型处理器采取保守方案,延期页表遍历直到之前内存操作完成,保证一致性但可能牺牲部分性能;推测性一致型处理器则基于性能优化策略,允许页表遍历提前进行,并在检测到一致性错误时触发回滚与重试机制。 这些检测机制通常依赖处理器内部的存储队列(Store Queue),在页表遍历加载地址前检查是否存在同地址的未提交存储指令。若有潜在冲突,遍历操作将被标记为失败,进而进行恢复。此类技术在Intel的P6及其后代架构(如Pentium Pro、Pentium 4、Sandy Bridge、Haswell等)中表现明显,同时也见于多代AMD K7以后的处理器。

相比之下,较新AMD架构如Zen 2则表现出无页表遍历一致性机制,导致在页表被修改时不进行自动无效化的代码存在风险。 在虚拟化场景中,TLB和页表遍历一致性问题尤其凸显。虚拟机监控器通常采用两级翻译——客体虚拟地址到客体物理地址,再到宿主物理地址。未启用嵌套分页时,虚拟化软件须维护“影子页表”,并借助页面保护并拦截页表修改,从而实现接近硬件一致性的TLB表现,但代价是每次页表更新带来巨大性能开销。相比之下,启用嵌套分页可降低此开销,但需更为复杂的硬件协议管理一致性。 研究表明,硬件一致性机制为操作系统的内存管理设计带来便利,减轻软件负担,提高系统稳定性和性能。

反之,非一致实现需要操作系统精细管理TLB无效化,稍有不慎可能导致系统崩溃或数据错误。至关重要的是,架构文档中对一致性的说明较为宽松,设计者及系统工程师必须结合实际硬件行为和测试结果,做出合理的设计和假设。 针对页表遍历的设计,不同处理器采取了不同策略。一些处理器通过强制所有页表遍历后置,保证其在先前的内存操作完成后展开,彻底避免数据竞争,但这种非推测模式可能影响高频访问的响应时间。另一些处理器则支持推测式页表遍历,在硬件层面增加检测与恢复机制,允许在发现不一致时快速回滚和重做,优化吞吐量与延迟。此类实现复杂但性能表现优异。

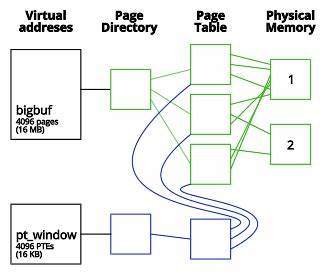

除此之外,相关工作还涉及如何快速修改页表条目以支持微基准测试。传统内核态访问页表的机制较慢,借助映射“页表窗口”等技巧,在用户态即可快速更新页表项,极大方便了相关性能测试和行为验证。 纵观当代x86处理器设计,TLB和页表遍历一致性机制直接关联着虚拟内存系统的稳定性和性能瓶颈。合理的无效化策略与硬件支持让操作系统更为健壮,而不断演进的硬件推测技术则平衡了性能和安全的需求。未来随着计算需求增长及规范的不断完善,内存管理机制将持续成为CPU微架构和操作系统研究的热点领域。 对研发人员、系统架构师以及安全研究人员而言,深入理解这些一致性设计不仅有助于优化软件性能,更可帮助识别潜在的安全风险。

正如近年来爆发的侧信道攻击等安全漏洞,微架构层的细节往往隐藏着重大的危害风险。TLB和页表遍历一致性研究无疑为此类探索提供了重要基础和思路。 总之,x86处理器中TLB和页表遍历的一致性问题体现了硬件与软件设计的微妙关系。通过严格的测试和对不同处理器的综合分析,业界得以更清晰地掌握内存子系统的运行特性,在设计高效、稳定的现代计算机系统时发挥了不可替代的作用。