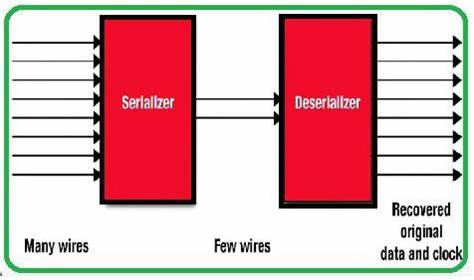

在现代高速通信领域,串行器/解串器(Serializer/Deserializer,简称SerDes)作为关键功能模块,承载着将并行数据转化为高速串行信号,及将串行数据重新转换为并行形式的重任。随着5G、物联网及数据中心等需求的激增,设计高效且成本可控的SerDes解决方案愈发重要。OpenSERDES作为一款基于开放硬件理念,采用Verilog硬件描述语言开发的SerDes项目,以其完全数字化可综合架构,成为行业内备受关注的开源设计之一。OpenSERDES项目基于Skywater OpenPDK 130nm技术平台,借助OpenLane和Cadence Virtuoso等先进EDA工具完成设计综合和仿真验证,具备高性能、易开发、灵活定制的优势。其采用标准CMOS工艺,极大降低了开发和制造成本,同时开放源码促使更多研发者能够协同创新,推动SerDes技术向更广泛的应用推广。OpenSERDES的结构设计紧凑而高效,主要由序列器(Serializer)、解序列器(Deserializer)、时钟数据恢复电路(CDR)、驱动单元以及数据采样单元组成。

序列器负责将输入的多路并行数据信号转换为单路串行数据流,紧接着通过高速通道进行传输。驱动电路采用了一系列CMOS反相器链路,确保信号在通道传输中具备足够的驱动力且信号完整性良好。接收端则配备了一个基于电阻反馈反相器(Resistive Feedback inverter)的前端感测模块,其在面对低幅度信号时具备优秀的灵敏度和抗噪声能力。随后该信号通过传统CMOS反相器进一步放大,完成初步恢复处理。时钟数据恢复模块采用过采样CDR架构,通过分析数据转换沿来动态调整时钟频率,实现高速串行数据流中的时钟同步,提高接收数据的准确率和时序稳定性。数据采样则通过主从锁存器(master-slave D flip-flop),利用从输入时钟中恢复的时钟信号锁存数据,准备进行并行解码。

主从锁存器模块以NAND门设计为基础,实现逻辑稳定且易于综合的存储单元。OpenSERDES项目的全部设计均采用Verilog HDL进行编码,设计文件结构清晰,易于社区共享与迭代。代码经过OpenLane工具链进行综合,实现了与Skywater OpenPDK 130nm的工艺兼容,确保电路布局合理,功耗受控。Cadence Virtuoso支持对设计的电路级仿真和版图验证,提升设计的可靠性和生产可行性。值得一提的是,OpenSERDES项目不仅提供了完整的设计源码,还附带了相关的gds、spice、netlist及oa文件,便于用户自定义仿真、工艺验证及后续封装制作。项目的模块划分细致,包含了针对基本逻辑单元NAND门的实现,锁存器DFF的实现,电阻反馈反相器设计,以及串行驱动器模块的详细设计,这种细粒度划分极大简化了学习曲线与后续定制。

开源硬件社区对于该项目的反馈积极,项目自发布以来获得了大量Star与Fork,展示了开发者与学术界对高性能、低成本可综合SerDes设计的强烈需求。通过开源共享,开发者不仅能够直接利用现有设计加速项目开展,还可以在此基础上优化电路性能,进行多样化应用探索,如高速通信链路、芯片间数据传输以及高速接口等场景。OpenSERDES作为一款基于标准CMOS工艺的数字型SerDes,兼具在教研和实际工业设计中的广泛适用性。它为高校、科研机构及初创企业提供了一整套可操作的设计方案,降低了进入高速串行技术领域的门槛。与此同时,该项目所示范的设计思路和方法,也为未来高性能SerDes设计树立了范例。随着技术进步,OpenSERDES有望结合更先进工艺节点及混合信号设计,进一步提升串行数据速率和系统集成度。

总之,OpenSERDES通过其基于Verilog的数字硬件实现、开放源码的共享模式及结合Skywater OpenPDK工艺的先进设计方法,展示了新时代高速串行通信模块的开发新路径。对于关注高速数字通信、芯片设计及开源硬件的相关领域人士而言,深入研究并应用OpenSERDES无疑能够获取技术积累和创新灵感。从实际操作角度出发,搭建OpenSERDES环境的过程相对友好,依托OpenLane自动化综合工具,开发者可以快速验证设计,降低前期设计门槛。此外,通过社区协作不断完善的设计文件和仿真资料,有效促进了设计质量和性能的稳步提升。未来,OpenSERDES在推动国产自主可控芯片设计和装备高速数据传输方面具有显著潜力,值得更多行业从业人员和学术研究者投入关注与实践。