中央处理器单位(CPU)作为计算机系统的核心组件,其设计复杂且极具挑战性。深刻理解CPU设计的基本原理,不仅有助于硬件工程师优化芯片性能,也使计算机科学爱好者更好地掌握计算机体系结构的核心机制。本文将系统地分析CPU设计的初步步骤,介绍传统CPU设计所需的关键因素,助力读者全面把握CPU的构造过程。 首先,了解CPU设计的背景和基本架构是至关重要的。传统的CPU通常采用冯·诺依曼架构,该架构将存储器和处理器区分开,指令和数据在存储器中统一管理。CPU通过指令周期完成计算任务,基本周期包括取指、译码、执行和写回阶段。

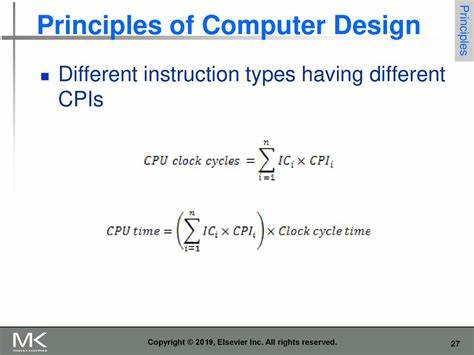

这些步骤串联组合,形成CPU的核心工作流程。设计时需要确保各个阶段协调高效,以实现指令流水线的最优化。 CPU设计的第一步是定义指令集架构(ISA)。ISA是CPU能够识别和执行的所有指令的集合,是软硬件之间的接口。设计合理的ISA能够平衡指令的复杂度与性能需求,从而发挥CPU的最大效能。通常,设计者需考虑指令的类型、操作数格式和寻址方式。

经典设计中,RISC(精简指令集计算)和CISC(复杂指令集计算)是两大主流指令体系,选择哪种架构直接影响后续设计的复杂度和效率。 紧接着,设计者需要搭建数据路径和控制单元。数据路径包括算术逻辑单元(ALU)、寄存器文件、数据总线和多路复用器等组件,负责处理数据流转和运算。控制单元通过译码器产生控制信号,驱动数据路径执行相应指令操作。数据路径的设计强调并行处理能力,减少数据传输延迟,而控制单元则不断监控指令状态,确保指令按序执行,且根据条件跳转实现程序流程控制。 此外,设计中的时钟频率和同步机制也是关键。

时钟周期定义了数据传输和指令执行的节奏。合理设置时钟周期时长,既需要考虑电路的物理限制,也要兼顾整体性能。同步设计确保各模块能准确按时完成任务,避免数据竞争和冲突,提升CPU的稳定性和可靠性。 为了提高性能,传统CPU设计中引入了流水线技术。流水线允许同时处理多条指令的不同阶段,如在执行某条指令的同时,可以提前取下一条指令,大幅提升指令吞吐量。然而,流水线设计带来了数据冒险和控制冒险的挑战,需要依靠转发机制和分支预测等技术解决这些问题,保障指令执行的正确性和连续性。

内存层次结构对CPU性能影响深远。设计时应合理配置高速缓存(Cache)和主存,提升数据访问速度。高速缓存作为CPU与主存之间的缓冲,减少访问延迟,提高整体运行效率。传统设计中,一级缓存(L1)通常集成在CPU芯片内,用于存储指令和数据,二级缓存(L2)则提供更大容量但相对较慢的缓存服务。设计优化缓存结构和替换策略,是提升CPU响应速度的关键环节。 现代传统CPU设计也重视寻找与功耗之间的平衡。

随着芯片制程工艺的进步,频率提升带来更高性能的同时,功耗增加成为限制因素。节能设计理念促使工程师在提升性能的同时,采用动态电压调整、时钟门控等技术降低功耗,延长设备的使用时间,并减少热量产生,确保硬件系统的安全和寿命。 集成度方面,CPU设计追求将更多功能模块集成到单一芯片上,如内置浮点运算单元、图形处理器以及专用加速器等,满足多样化计算需求。集成化设计有效缩短模块之间信号传输距离,减小延迟,提升整体处理效率。同时,这也对设计工艺和芯片布局提出了更高要求,需要精准的电路设计和强大的制造能力支持。 设计过程中,仿真和验证环节不可或缺。

采用硬件描述语言(如Verilog或VHDL)编写设计代码,通过仿真环境进行功能测试和性能评估,及时发现并修正设计缺陷,确保CPU设计的正确性。随着设计复杂度提高,自动化验证和形式化验证技术逐渐普及,大幅提高设计质量和开发效率。 总结来看,迈向传统CPU设计的第一步,涵盖了从指令集架构的定义,到数据路径和控制单元的构建,再到流水线技术的应用以及内存体系优化。每个环节都需兼顾性能、功耗和可靠性,才能设计出符合需求的高效CPU。伴随着技术进步与设计理念的不断创新,传统CPU设计仍将保持其重要地位,同时为未来计算架构的开发打下坚实基础。掌握CPU设计的基本原理,不仅有助于理解现有计算机系统,还为探索新一代处理器技术提供理论支持和实战经验。

。