随着科技的进步,生成式人工智能工具如ChatGPT在教育领域的普及给教学和评估带来了新的机遇与挑战。许多学生开始依赖这些智能助手来完成编程和设计任务,尤其是在复杂的数字设计和硬件描述语言(HDL)课程中。这种趋势给教师带来了巨大的压力,如何确保学生独立思考和真正掌握课题内容成为一个迫切需要解决的问题。本文将聚焦于如何通过设计高质量的RTL(寄存器传输级)设计考核题目,有效甄别并“过滤”依赖ChatGPT给出简单复制答案的学生,进而提升教学实效和学生的动手能力。 在传统数字电路设计教学中,学生往往需要独立完成模块的编码、调试和仿真,这一过程不仅考察设计能力,还检验对时序和流水线结构的理解。然而,对于依赖ChatGPT的学生来说,直接让AI输出一份看似合理的代码成为规避自主学习的捷径。

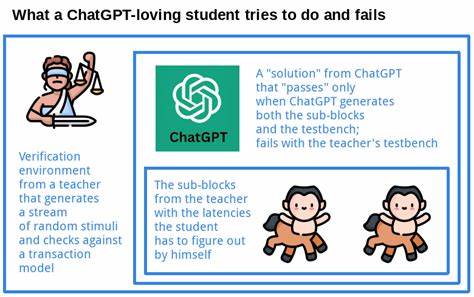

虽然AI生成的代码结构清晰,解决方案完备,但往往缺乏对任务潜在细节与时序约束的深入把握,致使其提交的代码难以通过严格的功能验证与测试平台。 针对这一现象,业内专家提出了一种创新的评测方式,即设计一道综合性高的流水线计算任务,要求学生利用预先提供的流水线子模块完成一个特定算术公式的计算。任务的难点在于子模块的具体流水线延迟未对学生明示,必须通过阅读代码或运行模拟才能正确推断。这种设计要求学生具备扎实的代码分析能力和实际验证经验,而非单纯依赖代码拼接或AI生成。 学生如果单靠ChatGPT提供的代码,因其对仓库代码的跨模块整合及流水线延迟的准确把握能力有限,往往无法通过严苛的测试环境验证。例如,任务要求持续处理连续到达的输入且不能有流水线堵塞或数据冲突,学生必须准确调整并同步不同子模块的时序,这远非标准代码生成工具所能自动实现。

此外,测试平台采用事务级模型,随机化输入数据及数据流间隔,大幅提高了验证的复杂度和真实性。 课堂中,部分学生尝试用AI生成全部子模块和测试平台,试图绕过设计要求,但此种方式明显违反课程目的。教师强调,完整的设计过程必须基于已有模块,强调模块复用能力以及在现有资源约束下完成系统设计。此类考核不仅体现了工业界设计流程,更引导学生学会严谨分析与系统思考。 在教学互动中,也不乏有学生针对AI帮助的界限提出疑问,甚至质疑此类设计任务与实际工作相关性。针对这些疑虑,专业人士指出,现代大型芯片设计如CPU、GPU和网络处理器的核心都是多个静态流水线运算单元的复杂组合。

掌握流水线设计和数据流控制是底层硬件工程师的基本技能,忽略这一部分将难以胜任工业需求。因而,课程设置需紧贴工业实际,提高学生的岗位竞争力。 教育界的共识是,必须尽早在大学课程中融入涉及流水线结构、流水控制和功能验证的微架构设计内容。结合当下功能验证技术,如事务级建模和自动化测试平台,提升学生发现设计边界条件和隐患的能力。此举不仅强化学习效果,更有助学生发现自我兴趣和能力的匹配,避免依赖工具照搬,培养独立创新精神。 除了技术教学意义,从教学管理层面,此类复杂考题自然成为过滤AI依赖的有效手段。

面对高度依赖ChatGPT的学生,考题设计的复杂度和严谨性迫使学生不得不亲自动手调试,深入理解设计步骤,显著降低了直接套用AI答案的可能性。 长远来看,随着AI的普及,单纯依靠传统作业或考试来评估学生不再可靠。教师应探索结合项目驱动和真实验证环境的课程改革,采用更加多元和动态的评估方案,促进学生全过程掌控,避免盲目依赖技术捷径。 针对依赖ChatGPT的学习瓶颈,学生本身也应调整心态,将智能工具作为辅助学习的辅助,而非作业的替代。完成基础知识的扎实积累和动手能力培养,是未来赢得职场竞争的不二法门。教育者应激励学生探索设计细节、主动寻求验证策略,积累经验,为未来芯片开发打好坚实基石。

总之,通过设计高难度且结合实际工业验证环境的RTL设计任务,教育者能够有效降低学生对ChatGPT的依赖,促进他们真正掌握数字设计的核心技术。深化流水线处理、功能验证技术的实践内容,将成为未来院校数字设计课程转型的重要方向,帮助学生在日益智能化的技术时代脱颖而出。各方应协同努力,共同推动产学研结合,促进硬件设计人才培养迈上新台阶。