在人工智能技术不断演进的今天,深度学习模型的复杂度和规模持续攀升,推动了对高性能计算硬件的强烈需求。传统的AI加速器多专注于张量计算能力的提升,而张量的预处理和数据重组等张量操作同样对整体计算效率产生巨大影响。针对这一痛点,Tensor Manipulation Unit(TMU)作为一种新兴的硬件模块应运而生,显著优化了张量数据的传输和变换过程,推动了AI系统芯片(SoC)迈入了一个崭新的高效时代。\n\nTensor Manipulation Unit是一种专为张量操作设计的可重构、近存内存(near-memory)硬件单元,旨在加速以数据移动为主的张量操作。其设计理念基于RISC(精简指令集计算)架构模型,赋予TMU灵活且通用的指令处理能力,能够支持包括张量转置、裁剪、拼接、维度交换等多种复杂的数据变换任务。传统处理器在面对这类数据搬运任务时,多依赖于通用计算单元和主存,潜在的内存带宽瓶颈和数据延迟成为性能瓶颈,TMU巧妙地通过近存内存技术将计算单元紧密融合至存储附近,极大缩短了数据移动距离和延迟。

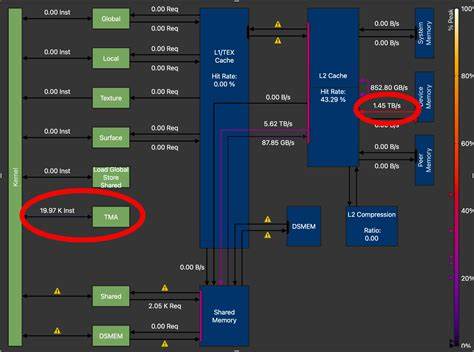

\n\nTMU的架构设计极具创新性,其仅占据极小的芯片面积,约0.019平方毫米,采用SMIC 40纳米工艺制造,实现了高密度和低功耗的硬件集成。通过双缓冲(double buffering)和输出转发(output forwarding)技术,TMU能够有效提升流水线处理效率,避免数据传输过程中的停顿和等待,确保高吞吐量运算成为可能。借助统一的寻址抽象,TMU具备极强的可拓展性和灵活性,使其不仅能支持粗粒度张量变换,也能覆盖更多元的细粒度操作需求。\n\n值得关注的是,TMU不仅独立作为张量操作加速器表现优越,其与张量处理单元(TPU)的协同集成更是展现出显著的系统级性能提升。在与自主设计的TPU系统集成后,整体AI推理的端到端延迟降低了34.6%,展现了TMU在大规模神经网络推理任务中的巨大实用价值。相比于传统的ARM A72处理器和NVIDIA Jetson TX2平台,TMU在操作级延迟上分别实现了1413倍和8.54倍的加速优势,这不仅反映了其在特定操作上的高效执行力,也彰显了其作为AI硬件生态重要组成部分的地位。

\n\n从应用场景来看,TMU具备广泛的适用性。现代AI推理任务广泛涉及多维度大量数据的变换与处理,如自然语言处理中的序列重组,计算机视觉中的图像特征变换,以及多模态AI中的跨域数据融合。传统软件驱动的数据操作易遭受内存带宽限制,且处理效率低下,而TMU的近存内存优势和可重构架构则显著缓解了这一瓶颈,为边缘计算、移动设备乃至数据中心都带来了性能与能效的双重提升。\n\n此外,TMU的设计理念也体现了当今AI硬件发展趋势中的一个核心方向——内存计算融合。随着芯片技术跨入纳米级制程,单纯依靠算力扩张已难以维持指数级提升,数据传输的瓶颈日益明显。TMU将张量数据变换卸载到靠近数据存储的位置,不仅降低了能耗,提升了响应速度,也为未来的异构计算架构铺平了道路。

它体现了硬件“专用化+灵活性”的平衡,使得AI SoC能够根据应用需求动态调整处理策略。\n\n从技术实现角度而言,TMU借鉴了RISC指令集的简洁高效,将张量操作抽象为一系列简明的内存至内存的数据移动指令,极大提升了指令执行的确定性和速度。统一的寻址方案不仅简化了硬件控制逻辑,也增强了对不同张量维度和格式的兼容性。这种设计使得TMU可以在不牺牲灵活性的前提下,实现高度定制的操作,加速多样的张量变换场景。\n\n纵观人工智能芯片发展历史,计算密集型任务获得了大量技术积累,而高效的数据管理和张量操作一直是性能提升的“隐形推手”。TMU的出现填补了这一空白,其引入的硬件级张量移动和逻辑重组能力,将成为AI计算体系结构中不可或缺的组成部分。

未来,随着神经网络模型的多样化和数据复杂性的增加,TMU及其类似架构将会在提升整体系统性能、能效优化和响应实时性方面发挥更为关键的作用。\n\n此外,TMU的研发和实测结果也为业界提供了宝贵的实践经验与设计参考。它显示出中小工艺节点亦能实现高性能的AI专用加速器,打破了大型制程或高功耗设计成为唯一路径的传统认知。硬件设计者可以借助TMU的设计范式,探索更多可重构近存内存模块,从而推动AI硬件架构迈向更加灵活高效的未来。\n\n在总结TMU的创新点时,不难发现它不仅仅是一个单纯的硬件加速器,而是代表了张量处理和移动方式的一次根本变革。其融合了灵活指令编程、存算结合、高效流水线和紧凑集成优势,能够为AI SoC带来更优异的广播性能和响应速度。

随着研究的不断深入和应用的持续扩展,TMU有望成为下一代AI计算平台的标配单元,引领智能硬件迈向更加智能化和高效能的新时代。