随着服务器和高级计算设备的飞速发展,处理器的计算能力不断增强,但真正让系统高效运作的关键,还依赖于输入输出(I/O)总线接口的高效设计和稳定运行。AMD Turin处理器作为新一代服务器级芯片,集成了丰富的SATA、USB和PCI Express接口,为高速数据传输和外设连接提供了有力支持。本文将结合Gigabyte MZ33-AR1主板展开深入探讨,解析AMD Turin平台上这些接口的端口映射方式、硬件架构、以及在固件层面上的初始化过程,帮助读者全面理解这一复杂生态。 首先,理解SATA和USB接口的重要性不可忽视。SATA接口长期以来作为硬盘和固态硬盘的主要存储连接通道,在服务器和NAS设备中仍扮演重要角色。虽然新兴的NVMe SSD已逐步通过PCI Express通道替代传统SATA驱动器,但SATA接口依然因其性价比高、兼容性好而广泛使用。

同时,USB接口以其强大的通用性,连接从存储设备、键盘、鼠标到摄像头和安全硬件的多样化设备,成为系统与用户间的关键桥梁。Gigabyte MZ33-AR1主板支持多达16个SATA端口,以及多组USB 3.x和USB 2.0端口,体现了其对丰富I/O能力的极大支持。 在实际工程中,确认每个物理端口是如何连接到处理器上的控制器,成为固件开发和系统调试的关键工作。通过在各个SATA和USB端口插入相应设备,然后借助Linux下的系统工具,如lsusb和dmesg,能够准确识别设备在总线中的位置,进而进行端口映射。这种方法不仅直观还极具实用性,既能识别USB设备所连接的具体根集线器,又能追踪SATA设备的控制器归属和端口编号。 针对USB端口的映射,Gigabyte MZ33-AR1配备了多种内部连接头,包括前端的F_USB3和F_USB2以及后置面板端口。

通过分别接入支持USB3.x和USB2.0的存储设备,利用lsusb以及层次化视图的lsusb -t命令,可以清晰刻画出USB拓扑结构和集线器排列。此外,主板上集成的美国MegaTrends公司的虚拟设备通过BMC(基板管理控制器)连接,为系统提供远程管理功能,也体现了现代服务器管理的复杂性和多层次性。最终确定了USB端口分别对应于PCI设备0000:e1:00.4和0000:42:00.4的两个独立的xHCI控制器。 SATA端口映射方面,过程同样基于Linux系统日志的分析。Gigabyte MZ33-AR1通过MCIO连接器提供了多达16个SATA端口,通常采购者可以通过MCIO转SATA线缆连接 SATA硬盘。为避免热插拔可能带来的不稳定性,建议每次换盘后重新启动并通过SCSI主机扫描触发系统识别更新。

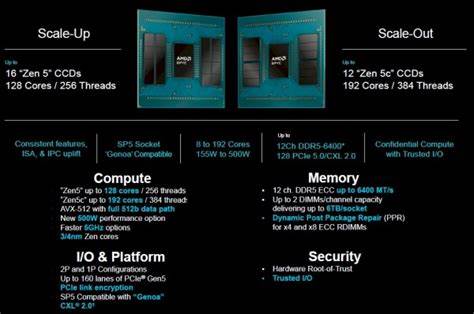

通过对不同MCIO端口的拨插,结合dmesg获取的设备日志,可以明确观察到SATA设备依次出现在ata3-5和ata11-13序号区间,分别隶属于PCI设备0000:43:00.0和0000:43:00.1。由此确认了不同MCIO连接器对应的SATA控制器分布。 更深入的理解需要对AMD Turin的PCI拓扑与物理架构展开分析。Turin平台内建多个PCI域,最多可达8个,每个域配合独立根桥实现I/O分割。lspci命令带参数输出可以直观地看到这些域及其包含的设备,诸如USB控制器、SATA控制器和其他外设。一台Turin CPU同时支持多个PCI根域的特点,促使固件及操作系统协调管理不同设备的初始化和分配。

一个核心挑战是Turin处理器内部高性能串行链路(SERDES)的组织。SERDES作为物理层接口,负责PCIe、SATA、CXL及多处理器互联的高速数据传输。Turin平台将128条物理链路划分为若干16条链路组,分别支持多种功能模式和可多路复用。链路分为"P"系列和"G"系列两类,其中"G"系列链路尤其负责CPU间互联(通过Infinity Fabric技术)。本质上,SERDES链路通过灵活配置,将物理链路绑定至PCI设备,用于不同I/O请求的实现。 与高性能计算密切相关的是NUMA架构设计,Turin处理器划分为四个NUMA节点,每个节点配备了对应的P和G链路。

根据不同的芯片设计,PCI域与P/G链路存在对应关系,尽管这种映射在官方文档中少有披露,但通过工程分析和端口测试,可以确认PCI域与P/G链路的对应逻辑,进而为端口参数配置提供理论依据。 实际系统构建当中,SATA端口对应的物理链路多多少少存在混合和异步现象,例如本案例中SATA控制器归属PCI域2,而物理链路G3链路实际属于PCI域1。这种架构上的复杂性显示出密集多层次硬件设计对固件初始化的挑战,以及对设计者深入理解芯片微架构的迫切需求。 针对SATA和PCIe链路的物理参数配置,Turin平台引入了MPIO架构,为高速链路类型声明、物理起止链路编号以及相关GPP(通用高性能端口)桥接信息提供了标准化描述。通过精确设定对应的起止链路号以及类型,固件可以准确引导底层硬件完成初始化,使得整体系统具备高效的链路激活和资源调用能力,提高I/O操作的稳定性和性能表现。 目前,基于Turin架构的系统固件支持仍处于完善阶段,关键模块如OpenSIL正在积极开发和更新,使CPU的初始化、PCI设备激活和I/O链路配置日益稳定。

尽管存在测试环境和硬件验证上的一定困难,但已有的成果表明,系统向完整支持多路SATA、USB及PCI Express接口的方向稳步前进。 总结来看,AMD Turin平台凭借其复杂的PCI域层级、灵活的SERDES链路配置以及先进的NUMA架构,带来了高性能与高度可扩展的I/O接口设计。通过对Gigabyte MZ33-AR1主板的实践映射,工程开发者可以深入理解各接口的物理与逻辑关系,为固件开发和系统优化提供坚实基础。展望未来,随着PCIe Gen5、USB 3.1及高带宽存储技术的成熟应用,Turin平台的接口能力将进一步释放,助力服务器与数据中心设备迈向更高效稳定的运行新高度。持续关注相关固件开发与硬件调试进展,将为系统设计人员带来更多宝贵的第一手实践经验和技术洞见。 。