递归神经网络(RNN)作为处理序列数据的经典模型,在自然语言处理、时间序列分析及信号处理等领域拥有广泛应用。然而,RNN的固有设计 - - 序列步步递归依赖,限制了其在GPU等并行计算硬件上的加速效率。传统的RNN训练流程以时间步长T为线性复杂度,导致长序列训练耗时较长,阻碍了模型大规模应用的性能提升。近年来,一种基于简化版循环单元结合并行扫描算法的技术,成功将RNN训练时间复杂度从O(T)优化至O(log T),为序列模型的GPU加速带来新的突破。本文将深入探讨这一创新实现,通过剖析minGRU和minLSTM的数学简化机制以及基于CUDA的并行扫描算法,分析其显著性能提升的背后原理及应用实践。传统RNN模型的核心瓶颈在于隐藏状态ht对前一时刻状态ht-1的强依赖。

以经典GRU为例,其门控机制明确包含对前一时刻输出的调用,使得无法将多个时间步的计算并行处理,只能沿时间维度顺序执行。此设计虽保证了时序信息的严谨传递,但却极大限制了在GPU这样天生适合大规模并行的硬件上发挥优势。每一步迭代的等待,使训练和推理过程速度受限,尤其在处理超长序列时,时间成本高昂,效率低下。为突破该瓶颈,研究者提出通过简化GRU和LSTM模型的结构,使其可以转化成线性递推关系形式。minGRU和minLSTM是两种典型的简化版本,核心思路是使各时间步的门控计算仅依赖当前输入xt,而不再依赖前一时刻隐藏状态ht-1。具体到minGRU中,将更新门zt、候选隐藏态h~t定义为仅依赖输入矩阵乘法的结果,不含递归依赖。

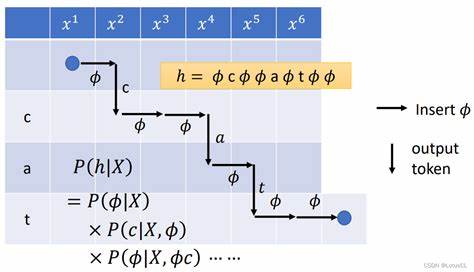

这使得一个复杂的时序递归过程,转换成了一个线性递推关系ht=at⊙ht-1+bt,其中at和bt均可并行计算,极大减少了顺序计算对硬件性能的限制。将RNN训练的递归过程转化为线性递推后,引入了经典的计算机科学并行扫描(parallel scan)算法,即前缀和操作的扩展版本。并行扫描算法能够利用结合律,采用树状结构计算方式,将序列递推深度由原先的线性O(T)降至对数O(log T)级别。这样的算法结构极为契合GPU大量核心的并行运算优势,能够大幅提升序列模型计算效率。具体实现时,将线性递推中的乘法加法序列抽象为二元变换的组合,通过Blelloch扫描算法的两阶段(上树归约与下树分发)步骤完成并行递归求解。此算法不仅加速了训练过程,还有助于扩展模型对超长序列的处理能力,兼顾数值稳定性和计算效率。

在实际实现方面,基于CUDA的并行扫描算法设计涵盖从门控参数提取到线性递归扫描的完整管线。为了最大化GPU利用率,设计者采用单核融合技术,将所有时间步的门控参数计算合并至一个大型内核,利用共享内存实现数据复用和缓存优化。这显著减少了内核启动开销和设备间数据传输,提升了访存效率。此外,扫描阶段采用高效的Blelloch算法定制内核,保证执行深度为对数规模,避免了传统循环所带来的性能瓶颈。通过这种内核级的深度优化设计,GPU并行化计算发挥极致潜力。为了评估该并行算法的效果,开发者在Intel i9-12900K CPU和NVIDIA RTX 4090 GPU平台上进行了详细的性能测试。

结果显示,针对短序列(T<2048),由于CUDA核启动和内存调度开销,传统CPU基于高度优化BLAS库的向量化实现在速度上偶尔更优。然而,随着序列长度增长,GPU并行扫描的优势逐渐凸显,特别是在超长序列(T≥8192)时,速度优势达到约2倍以上。具体体现在GRU和LSTM模型中,对于64K长序列的训练,GPU并行扫描明显优于CPU的线性扫描,体现出算法复杂度降低对实际计算时间的显著影响。性能分析工具NVIDIA Nsight Compute的核性能剖析揭示了实现过程中的关键优化点。最初阶段,门控参数提取内核是性能瓶颈,经优化融合与共享存储调整后,该内核执行时间占比大幅下降,且达到内存带宽饱和,说明数据访问瓶颈已被移除。新的性能瓶颈转向了最终的输出投影层,该层仍然以逐时间步单核执行为主,频繁的内核启动导致低占用率和带宽利用率。

未来进一步改进方案是将投影计算整合为单次大型矩阵乘法调用,借助cuBLAS等高性能库消除核启动开销并提升计算密度,期待带来更大幅度加速。该研究不仅从理论上验证了"Were RNNs All We Needed?"论文中的核心观点,也为传统序列模型的训练和推理性能提升提供了实用路径。通过算法创新与GPU底层优化结合,展现了改造旧有模型架构以适应现代并行硬件的巨大潜力。尽管miniRNN在某些实际任务上的精度表现尚无足够证据显示全面优于Transformer或其他架构,但在计算效率和模型简洁度方面,显然具备优势,适合在资源受限场景或特定数据集上尝试应用。技术发展趋势显示,在深度学习领域,各类模型架构因其不同的设计目标和计算特性持续繁荣。硬件适配性和算法并行化潜力成为衡量模型未来可扩展性的重要指标。

miniGRU和miniLSTM通过简化递归依赖,实现了计算复杂度的根本改善,为后续序列模型设计提供借鉴意义。同时,这一项目的实施经验也提醒研发者在实际GPU编程中,核融合、共享内存优化、避免频繁核启动等工程细节同样关键,决定了理论创新能否转化为真正高效的系统性能。未来可以预见,结合更多的并行算法设计与硬件加速方案,传统RNN与其变体有望在特定任务中重获新生。尤其是在模型普遍向大规模、长序列和低延迟方向发展的背景下,如何充分利用底层并行能力将持续成为研究的热点。与此同时,随着Transformer等架构不断完善和优化,序列模型领域竞争格局也将保持激烈,算法性能与模型表达能力的平衡将是一道永恒难题。总结而言,借助CUDA实现的RNN训练并行扫描算法,成功地将序列依赖的训练复杂度降至对数阶,显著提升了超长序列数据处理效率。

通过数学模型简化与并行算法巧妙结合,克服了传统RNN的顺序计算瓶颈,在GPU架构下展现了优异的加速效果。该研究不仅推动了计算机科学中的并行算法应用,也为深度学习模型性能优化提供了宝贵参考。对于从事深度学习与高性能计算交叉领域的技术人员而言,这一成果展示了理论与实践融合的典范,值得深入研究与借鉴。 。