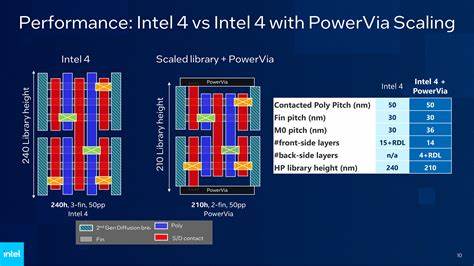

随着半导体行业的不断进步和创新,先进制程技术和内存架构的发展成为芯片性能提升的关键驱动力。Intel的18A制程作为下一代高密度逻辑制造节点,代表着晶体管缩小和电源管理技术的重要飞跃。同时,DRAM技术正面临4F2平面布局和3D堆叠设计的激烈竞争,背面供电技术(Backside Power Delivery)则在改善芯片功耗和性能方面展现出巨大潜力。本文将深入剖析Intel 18A制程的设计特征及制造成本,比较分析DRAM 4F2与3D技术的长远趋势,并探讨背面供电技术的采纳现状和未来应用前景。Intel 18A制程技术作为Intel计划中首次大规模采用背面供电技术的先进工艺节点,其核心理念是通过Gate-All-Around(GAA)宽带片层晶体管替代传统的FinFET以实现更小的晶体管面积和更高的开关性能。根据官方公开的资料,Intel 18A节点在SRAM布局面积方面取得了比Intel 3制程约30%的缩减,与目前业界领先的台积电N5和N3E工艺的0.0210微米平方面积相当,体现出极具竞争力的芯片密度表现。

这种显著的SRAM面积优化对整体芯片性能和功耗都有直接的积极影响,尤其是在缓存层级密集且性能需求高的处理器设计中。背面供电技术的采用是18A制程极具创新的亮点,它通过将电源供给电路设计在晶圆背面,减少了芯片正面的复杂走线和寄生电阻,显著降低了电源噪声和电压跌落问题。背面供电不仅优化了电源网络的分布效率,也为进一步缩短晶体管通路长度提供了可能。然而,背面供电的实现需要克服诸如晶圆背面抛光、激光穿孔和衬底感应等复杂工艺挑战,同时也对制造设备和产线自动化提出了更高要求,这也影响该技术的推广速度和成本结构。谈及成本,18A制程虽带来了显著性能提升,但采用复杂工艺的背面供电和GAA宽带片管技术,让其制造成本相较于前代节点有一定程度的增加。此类高复杂度工艺节点往往需要更高精度的光刻设备和多次的工序迭代,导致整体良率初期可能受到影响,成本回收周期较长。

尽管如此,18A的性能密度优势对于高端CPU和GPU市场来说,具备极大的吸引力。内存方面的革新同样令人关注。DRAM自诞生以来一直依赖不断缩小的单元尺寸来提高密度,当前主流的6F2布局已经发展多年,随着节点缩小至1d,技术瓶颈逐渐凸显。存储单元中的电容和控制晶体管的接触区呈现出了难以解决的缩小极限,这直接影响了制造良率和电气性能。SK海力士和三星等巨头提出了4F2架构,以应对6F2面临的物理极限。4F2利用垂直通道晶体管(VCT)和埋线(buried bitline)技术,实现了更短的电流路径和降低电阻,显著提升了DRAM单元操作速度和读写稳定性。

4F2架构通过纵向排列的存储单元设计,不仅减小了单元尺寸,也缓解了接触间隙狭窄导致的短路风险。然而,4F2技术对制程设备尤其是高纵横比刻蚀和金属沉积工艺提出了极高要求,现有设备是否能在保持良率的前提下实现大规模生产仍是行业关注的焦点。此外,4F2存在外设(peripheral)布局的两种选择——周边电路放在存储单元下方或者侧旁。前者通过硅晶圆的融合键合实现,类似于背面供电技术,但工艺复杂度较高;后者则通过混合键合技术连接独立制造的存储和外围电路层,要求极细微的键合间距,技术门槛很高。3D DRAM作为另一条路线,利用纵向堆叠的内存层实现更大容量和更高带宽。与4F2不同,3D DRAM不依赖高度复杂的光刻技术,更强调材料和硅互联技术的进步。

中国制造商在3D DRAM领域投入显著研发资源,部分原因在于其相对更低的对极紫外光刻技术的依赖,具备一定产业政策层面的优势。3D DRAM技术的挑战主要在于堆叠层间的热管理和互连延时问题。芯片内部热量的积累若未能有效散发,可能导致性能下降和寿命缩短,如何设计高效的散热结构成为关键。同时,多层级垂直互联对制造设备的精度和杂散电容控制提出更高标准。值得一提的是,Micron复兴的非易失性DRAM(NVDRAM)采用了铁电材料(HZO)和4F2架构,集成了钌(Ru)字线和CMOS电路于阵列下方。这种架构兼顾高密度与性能,并通过省略刷新周期来降低功耗。

虽然目前NVDRAM因成本较高难以取代传统DRAM在主流市场的地位,但其技术积累对未来DRAM工艺演进具有重要借鉴意义。回归背面供电技术,这一技术作为先进逻辑芯片提升能源效率和性能密度的关键手段,在Intel 18A节点获得了首度商业级应用机会。传统芯片设计中,电源网络复杂且布线层次繁多,电压降和电噪声问题日趋严峻。背面供电通过将供电层移至晶圆背面,显著缩短了电源传输路径,降低了寄生电阻和电容,进而提升芯片整体的能效比。这种设计理念也被部分DRAM架构借鉴用于peripheral-under-cell的周边电路布局中,需要通过融合键合技术完成前后晶圆的电气连通。当前背面供电技术的推广面临多个制约因素,包括异厂设备兼容性、加工标准化瓶颈以及多重制造流程的同步协作难题。

制造过程中涉及的晶圆翻转、深孔激光打孔(TSV)和精密测量技术均属于高难度工艺,短期内对产线的自动化和数据互联提出重大挑战。展望未来,半导体行业正在积极推动数字孪生技术的发展,从原子级模拟到晶圆级和制造厂(fab)级的数字孪生模型,为设计优化和产量提升提供强大支持。通过在虚拟环境中预测工艺路径和设备运行状态,企业能大幅缩短研发周期并降低试错成本,对未来如背面供电和复杂3D结构的制造提供保障。总结来看,Intel 18A制程及其背面供电技术的上市,将为逻辑芯片制造带来里程碑式的提升。与此同时,DRAM市场技术路线正在4F2平面布局和3D堆叠方案之间展开博弈,双方各有优劣,在性能、密度、生产复杂度和成本之间寻找平衡。背面供电技术被视为提升芯片能效的关键创新,但其广泛应用仍依赖产业链成熟与工艺标准化的推进。

未来,结合数字孪生模拟、先进材料研究以及多维度设计集成技术,半导体行业有望持续突破物理极限,打造出更高效能、更高密度且制造更经济的芯片产品。