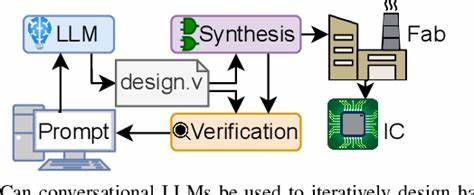

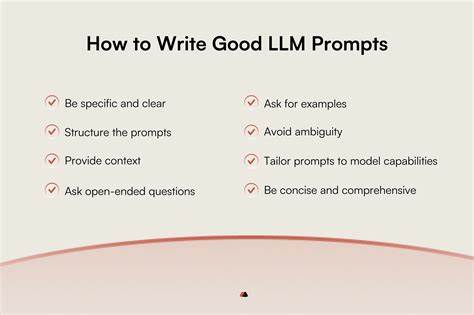

随着人工智能技术的飞速发展,硬件设计领域正经历着一场由对话式人工智能模型推动的深刻变革。传统硬件设计流程繁琐且对工程师编码技能要求极高,设计者需要将自然语言规格转化为硬件描述语言如Verilog代码,整个过程复杂且易出错。然而最近由OpenAI的ChatGPT、谷歌Bard等大型语言模型(LLM)引领的对话式人工智能展示了在程序生成领域的强大能力,硬件设计也因此成为AI技术的全新应用前沿。论文《Chip-Chat: Challenges and Opportunities in Conversational Hardware Design》(2023)通过对话式LLM与硬件工程师合作开发8位累加器微处理器的案例,首次实现全AI生成的硬件描述语言代码成功进入芯片制程,展示了该领域前所未有的创新潜力。这一突破不仅进一步确认AI辅助硬件设计的可行性,也揭示了现阶段仍需克服的诸多挑战,以及未来的良好发展机会。传统硬件设计依赖大量工程师经验和手工流程,易受人为失误干扰。

规范准确的转码工作需要熟练掌握硬件描述语言的语法和时序逻辑,还要结合实际芯片工艺约束进行反复验证,耗时耗力。与之相对,利用对话式大型语言模型将自然语言指令直接转化为硬件代码,极大缩短设计周期,提高迭代效率。这种技术能够让设计者用更直观的方式与AI展开多轮交互,不断调整并优化设计方案,从而降低学习门槛并减轻重复劳动的负担。然而目前促使语言模型适应硬件设计的最大难题在于硬件领域的专业性和复杂度极高。硬件描述语言对精确时序、资源布局和功耗管理有严格要求,其语义和结构与传统编程语言截然不同。大型语言模型虽然在通用代码生成上表现优异,但尚缺乏对硬件设计规范的深度理解和验证能力。

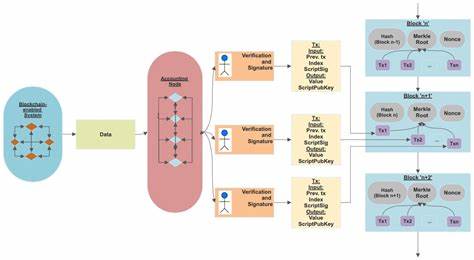

这就导致直接输出的代码可能包含逻辑漏洞、性能瓶颈或不符合工艺规则,必须由经验丰富的工程师反复调试。Chip-Chat项目正是在这样的背景下展开,研究团队通过与LLM反复“对话”,引导AI理解特定硬件架构需求及约束,最终成功合成了一个基于8位累加器架构的微处理器硬件描述代码。值得称道的是,该设计顺利流片至Skywater 130nm工艺,成为全球首个完全由AI撰写硬件描述语言完成流片的案例。这标志着AI协助硬件设计已从理论验证迈向实际应用,具有里程碑意义。不仅如此,这种协同设计方式大大激发了硬件领域的创新活力。工程师能够利用对话式平台快速试验不同架构思想,语言模型则负责生成初步代码并执行规范校验,使得原先耗费数月的设计流程可压缩为数周或更短时间。

这对快速迭代、高效原型开发极为关键,为芯片创新注入新的动力。此外,AI在硬件设计中的应用还蕴含广阔的商业化前景。随着芯片定制化需求攀升,能够支持自然语言输入的智能设计助手对于中小企业和初创团队尤为重要,它们通常缺乏雄厚的硬件工程资源。借助对话式大模型驱动的自动化设计平台,将极大降低芯片开发门槛,促进更多创新型产品问世。在政策与生态层面,也值得关注相关标准制定和安全风险管控。硬件代码的正确性和安全性直接影响芯片性能和系统稳定性,盲目依赖自动生成代码则可能带来不可预见的安全隐患。

因此,未来必须发展基于AI生成代码的严格验证与测试工具体系,确保设计质量和供应链安全。总体来看,Chip-Chat这一里程碑案例充分展示了对话式硬件设计的巨大机遇与现实挑战。大型语言模型为设计师搭建了全新沟通桥梁,降低门槛并提升效率,同时也暴露出当前技术对专业硬件知识的理解不足和验证难题。未来,通过模型训练优化、融合物理验证方法以及交互设计创新,AI辅助硬件设计有望成为芯片开发的常态。它不仅能助力硬件行业实现更智能、更快速和更低成本的设计流程,也将在推动电子产业持续创新与生态多元发展中发挥关键作用。面对人工智能技术不断突破的时代,硬件工程师与AI协同共创的对话新篇章正在展开,迎来智能硬件设计新时代的曙光。

。