随着多核处理器的普及和并发编程的复杂性不断提升,程序员对内存模型的理解和应用变得愈发重要。C/C++11引入了全新的内存模型规范,试图为并发程序设计提供理论保障,确保不同线程对共享数据的访问不会出现未定义行为。其中,顺序一致性(SC)作为最强的内存一致性保证,理应为开发者提供简洁清晰的程序语义。然而,最新研究发现,C/C++11标准中SC原子操作的语义存在严重的设计缺陷,导致基于该模型的多种编译优化和机器代码生成存在安全隐患。针对这一问题,学术界提出了修复版本RC11,旨在完善顺序一致性的设计,恢复其理论与实践中的一致性和正确性,为高性能并发程序提供坚实保障。C/C++11内存模型规定了多种内存访问模式,从放松的relaxed到强制性加载和存储顺序的SC,满足不同性能和安全需求。

SC访问应当确保程序中所有线程看到的操作顺序与程序代码中出现的顺序一致,实现直观的"原子性"行为。传统理论认为此模型具有数据竞争无顺序一致性(DRF-SC)保证,即若程序仅对SC原子操作发生竞争,则执行结果不会违反顺序一致性。然而,新研究指出,C/C++11规范描述的SC语义在针对弱架构如Power和ARMv7的编译方案中存在漏洞,具体表现为生成的机器代码不能完全保证程序所需的顺序一致性。这导致编译器对某些SC原子操作的重排序和优化会引发难以调试的竞争条件和错误,严重时破坏程序的正确性。核心问题主要集中于几个方面。首先,现行设计允许过度消除SC访问操作,导致编译后程序的执行结果与标准语义不符。

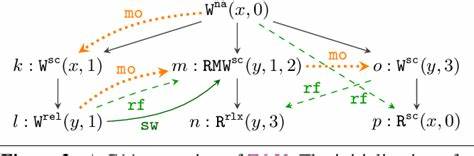

其次,SC屏障指令(Fence)语义弱化,导致无法有效阻止无序访问。这些缺陷使得针对弱内存模型的处理措施不足,不能完全屏蔽来自硬件的复杂状态转换。更严重的是,这些缺陷助长了"凭空读取"(Out-of-Thin-Air Reads)现象的出现,即程序读取了本不应存在的内存值,极大危害代码的可预测性。针对上述缺陷,研究团队提出了RC11(Repaired C11)模型,基于C11内存模型做出结构性改进。RC11强化了SC访问的语义,增加了必要的约束,避免无意识的操作消除;同时恢复了Fence的累积性,使其能够有效串联多个线程间的操作顺序,阻止不良重排序。此外,RC11引入了更严格的规则来杜绝凭空读取,确保程序运行中仅能产生符合逻辑的内存状态。

RC11的引入也带来了针对不同处理器架构的编译策略调整。对于x86-TSO架构,其较强的内存顺序保证使得SC访问的编译较为直接且可靠。针对弱内存模型如Power和ARMv7,RC11提供了经过形式化证明的新的编译方案,确保由于硬件的弱保证而造成的重排被恰当控制。这些编译方案中关键在于合理插入强Fence指令,维护Load-to-Store顺序,避免薄弱Fence所可能引发的顺序失效。此外,RC11还支持程序转换的正确性证明。理论证明指出,在遵守RC11模型约束的前提下,复杂的程序优化和转换不会破坏SC的语义,确保高效编译同时不牺牲程序安全。

显著的是,RC11保留并强化了DRF-SC的保障,使得合规程序在无数据竞争时,仍能享受简单的顺序一致执行结果。从程序员视角而言,采用RC11能够获得更稳定且有保证的并发语义。它不仅提升了对多线程同步设计的信心,还为复杂的同步原语实现提供理论支持。结合现代硬件特性,RC11鼓励合理使用Fence和SC操作,避免不必要的性能浪费,同时减少因弱内存模型引发的隐蔽Bug的风险。一些典型示例展示了修复前后模型对程序行为的影响,佐证了RC11在解决诸如读后写依赖消除失败、SC读写之间顺序失效等问题上的优势。整体来看,RC11的提出为C/C++11的内存模型注入了更多理性和严谨,解决了多年来困扰并发程序设计者的关键难题。

它不仅增强了模型的理论完备性,也为硬件厂商和编译器开发者提供了更加明确的指导原则,加速安全并发技术的发展。未来,随着硬件架构日益复杂,编程语言对内存一致性的需求不断升级,像RC11这样的修复和完善显得尤为重要。研究者们继续探索更高效、更灵活的内存模型,以期在保证程序正确性的同时,最大化硬件利用率和并发性能。程序员在选择并发工具和设计多线程程序时,也应密切关注内存模型的发展动向,结合实际应用需求,选择合适的原子访问级别与同步策略。掌握与遵守严格且清晰的模型语义,是提高软件可靠性和降低维护成本的关键所在。总结而言,C/C++11内存模型中顺序一致性的修复,不仅是理论上的革新,也是实务中的必然。

RC11为SC原子操作定义了一个更加稳固和安全的框架,保障了多架构环境下的编译正确性和程序执行的理想行为。通过理论与实证结合的方式,这一工作拓宽了现代并发程序设计的疆界,推动编程语言拥抱未来硬件的多样化特征和复杂挑战。 。