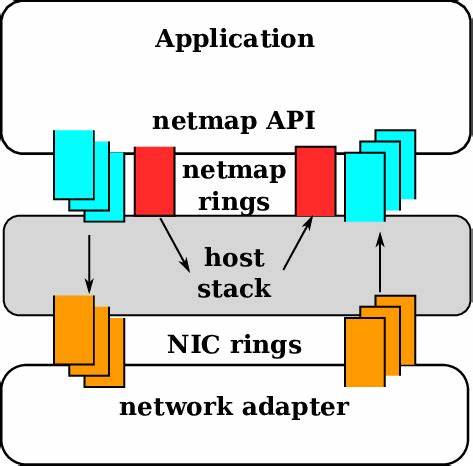

随着现代网络应用对高性能数据传输的需求不断增长,网络接口卡(NIC)在数据处理链路中的作用日益关键。CPU通过每核的接收环(Rx环)实现数据包的并行处理,然而这些接收环的设计和运行机制也带来了意想不到的性能瓶颈。深入理解NIC接收环的双重角色及其影响,有助于推动网络系统的优化,提升整体吞吐量和响应效率。 传统网络架构中,每个CPU核心都会配备独立的接收环,目的是并行处理从网络接口卡接收的数据包。这些接收环通常被设计得足够大,以容纳高达数千条条目的数据包缓冲,确保在流量激增时不会丢包。然而,这种设计往往导致一个关键问题,那就是系统的I/O工作集远远超出CPU最后一级缓存(LLC)的容量,进而引发严重的内存带宽压力和性能下降。

最近的研究尝试通过"shRing"机制来缓解上述问题。该机制通过多个CPU核心共享接收环,显著减少了I/O工作集的大小,理想状态下能减轻内存带宽的负担,加强缓存利用率。然而,shRing在负载不平衡的实际场景下表现并不理想。负载不均会导致部分核心成为瓶颈,限制整体系统性能的提升。 根本原因在于接收环承担了两个独立且正交的生产者-消费者结构。一方面,内存分配环节中,CPU核心负责产生空闲缓冲区,这些缓冲区随后被NIC用来存储接收到的数据包。

另一方面,数据传递环节中,NIC生成实际的网络数据包,交由CPU核心消费处理。 这种两个结构的交织导致了资源管理和数据处理的复杂性,阻碍了系统在负载变化时灵活调配资源的能力。换言之,内存分配和包传递两部分绑定在一条接收环中,限制了缓冲区在核心间的高效流动,造成性能瓶颈。 为此,研究团队提出了创新的CPU-NIC接口设计 - - rxBisect。该方案通过将传统单一的接收环拆分成两条独立的环路,分别对应内存分配和包传递两个环节。这样,内存分配过程可以与数据包的接收完全解耦,允许空闲缓冲区在CPU核心间自由传递,极大地增强了负载均衡能力。

rxBisect的实施不仅在理论上优化了内存资源管理,更在实际软件仿真测试中展现出卓越的性能提升。相较目前主流方案shRing和传统每核独立接收环,rxBisect分别带来了高达20%和37%的吞吐量提升。这意味着网络应用在高流量和复杂负载环境下,能够保持更稳定和高效的运行状态。 此外,rxBisect的设计理念为未来多核高性能网络架构提供了新的思路。通过合理分离不同功能模块,系统可以更加灵活地适应各种应用场景的需求,包括云计算、大数据分析、边缘计算和实时通信等领域的高速数据处理。 总结来看,网卡接收环的双重功能虽服务于数据吞吐和内存分配两大重要任务,但如果无法有效协调,反而成为性能瓶颈。

rxBisect创新地拆分这两者,解放了资源流动的灵活性,为网络系统的性能优化提供了实证支持和创新思路。随着网络技术持续演进,理解和优化这类基础组件的设计,将成为推动整体网络性能升级的关键因素。未来的研究还可以基于rxBisect框架,探索更加智能化的资源调度算法和硬件支持,进一步释放数据处理潜能,实现更为高效和可靠的网络基础设施。 。