随着科技的不断发展,处理器性能的提升不仅仅依赖于单核速度,更强调多任务并行处理能力。内存级并行性(Memory-Level Parallelism,MLP)作为衡量处理器同时处理多个独立内存操作能力的重要指标,成为评估现代SoC设计性能的关键。苹果公司近年来推出的M系列芯片,例如M2与后续的M4,是当前消费级ARM架构中的佼佼者,其内存级并行性的表现尤为引人关注。本文将聚焦苹果M2与苹果M4在内存级并行性上的差异,分析两者的技术演进及实际性能表现,为用户理解和选择设备提供指导。 苹果M2芯片于2022年发布,基于先进的ARM架构设计,采用统一内存架构(Unified Memory Architecture,UMA),使CPU与GPU共同访问同一内存资源,极大地提升了数据传输效率和整体响应速度。M2所搭载的LPDDR5内存为系统提供高速带宽,满足高强度的计算需求。

相比之下,M4则在2024年问世,延续了统一内存架构的设计理念,然而升级为性能更优的LPDDR5X内存,理论上提供更高的内存带宽,有助于处理大规模、多线程任务,并进一步发挥处理器的内存并行潜力。 内存级并行性本质上衡量的是处理器在面对多次内存请求时,能够同时保持多少未完成的请求。现代处理器需要应对大量随机存取操作及数据结构中的指针跳转,这种情况下的延迟很难通过单一请求的优化消除,因此提高内存请求的并行处理能力显得尤为重要。高内存级并行性意味着处理器能够发起更多重叠的内存请求,在隐藏单次请求的高延迟基础上提升整体处理吞吐率。 评估内存级并行性的一个常用方法是“指针跳跃”基准测试,通过构造一个巨大的索引数组,形成环状的指针链表,实现随机访问模式。这种模式模拟了日常软件中经常出现的链式数据结构访问,特别是需要反复跟踪指针指向的数据的场景。

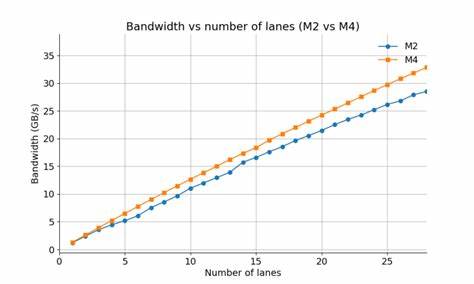

该基准从一个元素开始,读取其中的数值后跳转至对应的索引位置,如此循环遍历整个数组。由于每次访问的地址不可预测,这完全考验了处理器的并行访存能力和缓存系统的响应效率。 为了更细致地揭示多线程环境下处理器的内存并行能力,测试中将单条指针链划分为多个“通道”或称为“车道”(lane),比如两条、四条甚至更多条链路同时访问。这种多轨道访问大幅提升同时进行的内存操作数量,从而推测出处理器可持续支持的最大并行内存请求数。研究中,苹果M2与M4在最多28个车道的测试下均表现出较好的支持能力,在近30个同时活跃访问下能够保持稳定的数据吞吐率。 通过指针跳跃测试的传输速率,结合每次访问一条缓存线大小(128字节)的假设,可以推算出有效的内存带宽。

测试结果表明,苹果M4相比M2在单核随机访问任务中约提升了15%的性能,这一提升虽不算巨大,但足以反映新型内存技术LPDDR5X的优势及芯片架构优化带来的效益。值得注意的是,两款SoC都能较好地维持高并行访存状态,说明苹果在设计内存子系统时重视多任务并行处理能力,满足现实复杂场景的需求。 在实际应用环境中,内存级并行性的提升可以带来多方面的性能改进。例如,运行大量随机访问型数据库查询、动态数据结构操作及多线程网络服务器时,处理器能够更好地利用内存带宽,减少因等待数据加载造成的空闲周期,提升整体处理效率。同时,图形渲染、机器学习等领域也受益于高效的内存并行能力,尤其是在GPU与CPU统一共享内存的架构下,这种性能优势更为明显。 虽然苹果M4相较M2有所进步,现有测试也暴露出当前架构对于内存并行数目存在一定物理限制,超过28条并行访问的测试结果噪声较大,难以准确评估更高并行度的性能表现。

原因之一可能在于硬件资源瓶颈,如地址转换缓冲(TLB)和缓存层级设计,亦可能涉及芯片内部控制机制对过度并行请求的调节。此外,操作系统层面的内存管理策略、页面大小(Apple设备中使用较大页面减少TLB压力)等也对并行能力产生影响。 针对更高阶内存并行性能的探索,业内专家建议采用底层汇编程序结合微架构性能计数器进行细粒度分析,不过由于苹果尚未公开M4内部架构详图,这限制了研究者的深入调查能力。目前仅有M1部分逆向工程资料,M2和M4的内部细节仍依赖外界持续测试和推测。 综合来看,苹果M2与M4在内存级并行性上的表现均属领先水平,满足了现代多任务和复杂内存访问场景的需求。M4虽然在硬件和内存技术上有所进化,但实际性能提升保持在合理范围,反映出芯片设计在功率效率与性能之间的平衡取舍。

未来,随着芯片设计和内存技术的不断突破,内存级并行性仍将是处理器性能提升的重要方向,特别是在移动设备对高性能低功耗处理的需求越来越高的趋势下。 对于开发者和终端用户而言,理解内存级并行性的意义有助于优化软件性能和选购硬件产品。编程时,设计更适合并行访问和减少内存访问延迟的算法,可以充分发挥苹果芯片的潜力。选购时,关注处理器支持的内存技术和系统整体架构,可以帮助获得更为流畅和高效的使用体验。 展望未来,苹果及其他芯片制造商可能会继续推陈出新,采用更先进的内存管理策略和技术,提升内存级别并行性及系统整体响应速度。随着人工智能、大数据分析和复杂图形处理等任务的兴起,内存级并行性已经成为衡量处理器性能的核心指标之一。

对比苹果M2与M4的研究不仅体现了技术的进步,也为行业发展指明了方向。用户可期待未来的Apple Silicon继续在性能与能效之间取得更优平衡,带来更加卓越的计算体验。