随着半导体行业的不断发展,芯片制造工艺的进步成为推动科技创新和性能提升的核心驱动力。英特尔近期在日本VLSI研讨会上披露了其备受期待的18A制程技术,展现了令人瞩目的性能优势和节能改进。作为继Intel 3之后的新一代制程节点,18A不仅在速度上实现了高达25%的提升,同时在功耗方面也带来了近40%的显著下降,这无疑为计算芯片的未来发展注入了强劲动力。 英特尔18A制程技术的核心创新是引入了Gate-All-Around(GAA)晶体管架构与PowerVia背面供电网络的结合。传统的芯片设计通常采用前置供电方式,这限制了互连线的布局和晶体管密度。而PowerVia技术通过将电源线路移至芯片背面,不仅释放了前端互连层的空间,还使得关键互连层的线距得以收紧,从而提升了芯片的信号传输效率和整体电气性能。

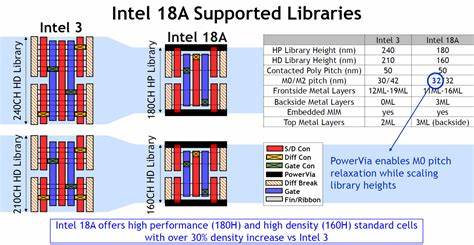

这种新颖的金属堆叠结构为提升制程良率和简化制造流程提供了极大便利,进一步降低了生产难度与成本。 在标准化功率、性能和面积测试中,基于Arm核心子模块的测试结果显示18A制程在相同性能功耗下,相比Intel 3提升约15%的性能表现。当电压维持在1.1伏特水平时,时钟频率可实现高达25%的提升,且无额外能耗增加;在约0.75伏特低电压运行时,则能达到18%的性能提升或实现接近40%的功耗节省,展现了优秀的功耗与性能平衡。 18A工艺在晶体管设计和版图尺寸上也进行了显著优化。其高性能调校型单元高度仅为180纳米,高密度设计单元更缩减到160纳米,均较前代产品有所缩小。前端金属层数由Intel 3的12至19层减少至11至16层,同时新增的三层背面金属层为PowerVia供电提供支持。

互连层M1到M10的线距从最高60纳米缩紧至32纳米后,又在上层有所放松,令整体线路设计更加合理。全新的低数值孔径EUV曝光技术应用于M0至M4层,不仅极大减少了44%的掩膜数量,也简化了曝光工艺流程,为大规模量产保驾护航。 英特尔计划采用18A制程技术打造低功耗的“Panther Lake”计算芯片模块以及仅配备高效核心的“Clearwater Forest”Xeon 7系列服务器处理器。为了满足不同市场的需求,英特尔还将推出三种版本的18A方案,包括成本优化的17层版本、均衡的21层版本以及面向高性能市场的22层版本,灵活调整以覆盖从移动端到数据中心的多样化应用场景。 面对激烈的行业竞争,英特尔18A的发布无疑展示了其在先进制造技术领域的决心和实力。在业界普遍关注台积电2纳米工艺的当下,英特尔以创新的设计理念和独特的背面供电网络回应挑战,力求实现性能和功耗的平衡突破。

虽然市场对英特尔能否迅速大规模量产18A制程产品持审慎态度,但已有的工艺优化和早期试产示范产品表明,英特尔有望在2025年下半年迎来技术量产的关键时刻。 从长远来看,英特尔18A制程技术的成功推行不仅将赋能其下一代CPU和GPU产品,还将推动整个计算生态的进步。更紧凑的晶体管布局与更高效的供电设计意味着未来芯片可以实现更高的集成度和更低的功耗,从而为人工智能、大数据分析、云计算等高性能计算领域带来实力提升和能耗减负。 此外,18A技术中采用的PowerVia背面电源传输方式,为行业后续制程演进提供了宝贵经验和参考,未来有望在更先进的节点中普及开来,推动半导体产业制造架构的深度重塑。 相较于以往英特尔在先进制程节点过程中遇到的挑战和延迟,18A制程的稳定进展和创新优势为其重塑市场信心铺平道路。尽管有声音质疑英特尔是否能在竞争激烈的制程赛道上持续领先,但从此次技术展示来看,英特尔正在以实际技术实力回应质疑,为芯片设计者和终端用户带来更多期待。

总体而言,英特尔18A制程技术凭借性能提升25%、功耗降低近40%的显著优势,结合背面供电改进和GAA晶体管的革新设计,标志着制程工艺迈入新纪元。随着量产的临近,18A有望成为驱动未来计算平台高性能与节能协同进化的核心基础,推动智能终端和数据中心实现更优表现和更低能耗的完美平衡。半导体行业的未来发展仍然充满竞争与机遇,而英特尔18A无疑为这一波技术革新浪潮注入了不可忽视的强大动力。