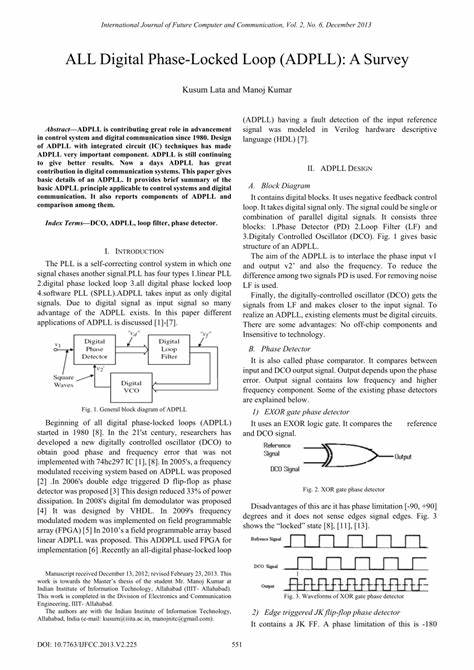

在低频引力波探测、星间激光干涉和高精度光学测量领域,相位测量系统(Phase Measurement System, PMS)承担着把皮米级位移转换为微弧度级相位信息的重任。传统模拟方案与基础的IQ解调方法在面对数十兆赫兹、极低光子数和苛刻噪声预算时往往力不从心。全数字锁相环(All-Digital Phase-Locked Loop, ADPLL)以其数字化、抗干扰强、可扩展性高的优势,已成为空间激光干涉相位读出(如LISA、Taiji、TianQin等)和地面精密测量的主流解决方案。本文结合最新研究与FPGA实测结果,深入解析ADPLL的工作机理、环路参数设计、关键噪声源及工程实现要点,为实现高带宽与高精度并重的相位计提供明确的设计路径和实践建议。 全数字相位计的核心是将输入的高频异频信号通过ADC采样后,与数字本地振荡器(NCO)生成的正交参考信号分别相乘并低通滤波,得到I、Q两路基带信号。Q通道在小相位误差条件下近似与瞬时相位误差成正比,经过比例-积分(PI)控制器形成对NCO的频率与相位驱动,从而实现相位锁定。

NCO内部由相位加法器(PA)和相位增量寄存器(PIR)构成,PIR反映瞬时频率,PA反映瞬时相位,二者既是环路的执行量,也作为最终读出端口提供测量数据。 在星间激光干涉中,PMS需满足在3 mHz至1 Hz带宽内将自身噪声控制在约1 pm/Hz的位移等效值,对应约6 µrad/Hz的相位噪声要求;输入异频可能随着多普勒效应在5-25 MHz范围内漂移。要在如此苛刻条件下既保证环路稳定性又实现足够带宽以追踪频率变化,需从环路增益、带宽、相位裕度、时延和量化位宽等多方面统筹设计。 从控制理论角度看,ADPLL的开环传递函数可以在z域描述,经后向欧拉(backward Euler)映射到s域后,近似为一个二阶二积分器(type-II)闭环系统,其动态由自然频率wn和阻尼比ζ决定。目标闭环带宽wbw、采样率fs、输入信号归一化幅值A和环路时延D共同作用决定PI参数KP与KI的取值。为便于硬件实现,通常将KP和KI实现为2的幂次位移(即用位移实现乘法),这既节省FPGA资源又利于数值稳定性。

设计流程建议先确定fs与A,给定目标带宽与预设阻尼(工程上常取ζ≥1以对抗数模滤波与计算延迟引入的相移),按解析公式估算KP与KI,再设计低通滤波器并计算其在目标带宽处的相移,最后计算总时延带来的相位裕度并微调滤波器与增益以满足稳定性与相位裕度要求。 环路带宽是精度与响应速度之间的核心权衡。带宽增大能够更好地抑制输入相位噪声(例如激光频率噪声经异频转化后的相位贡献),但同时会将更多的加性噪声(光电转换的散粒噪声、电子噪声与激光强度噪声)耦入到环路读数中。对于典型的空间任务,例如在LISA的接收光功率约700 pW条件下,理论与数值评估显示总相位误差的方差随带宽变化呈现"凹形"曲线:存在一个最优带宽在加性噪声和输入相位噪声之间取得平衡。根据实际噪声模型与实验参数,LISA场景下该最优带宽约为200 kHz,Taiji约为250 kHz,而对接收光功率更高的任务,带宽可以更大以进一步降低输入相位噪声残余。 对ADPLL性能影响显著的噪声来源可以归纳为三类:输入信号噪声、NCO相关的截断与量化噪声、以及PA/PIR的读出量化噪声。

输入相位噪声包括激光频率噪声与任何来自光学链或电子链的相位抖动,这部分噪声通过误差传递函数E(f)=1/(1+G(f))被环路在带内抑制。输入的加性噪声并不直接是相位,但在相位检波过程中等效为相位抖动,其大小与噪声功率谱密度与载波幅度比成比例。 NCO内部的截断噪声可以分为频率截断(PIR位宽截断导致的频率分辨率噪声)、相位截断(PA截断引入的相位噪声)以及幅度量化噪声(数字查表生成的正弦波幅度量化)。理想的截断等效为对信号加入白噪声,其功率谱密度与截断位数呈指数关系。为了避免截断带来的周期性伪谱,工程上常对截断前信号加入抖动(dither),推荐使用三角分布抖动以使截断噪声近似为白噪声,从而把窄带相位伪谱转换为平坦噪声底。尽管环路的误差传递函数可在带内抑制PA与PIR截断噪声,但在读出端位宽不足时,读出噪声会直接成为最终相位测量的极限噪声。

读出噪声是最终用户最关注的指标之一。PIR代表瞬时频率,其读出分辨率与PIR的位宽直接相关;PA代表累计相位,因其在时域上呈快速溢出(sawtooth)特性,通常需要在多通道或差分读出前进行恰当的处理。理论与FPGA实测结果均给出明确的位宽建议:为满足微弧度级的读出需求,PIR位宽需达到约38位或更高,而PA的读出位宽建议不低于7位。幅度量化位宽则影响NCO幅度引入的相位噪声,工程上建议幅度量化不小于5位,但在实验中为了获得更好的噪声裕度通常选用更高位宽(例如10至12位)以避免幅度量化噪声成为主导源。 为了验证模型与位宽限制对实际相位噪声的影响,研究团队在FPGA上实现了目标带宽约200 kHz的ADPLL,并采用一种改进的数字分配测试方法。通过在FPGA内部用NCO生成一对完全相同的测试信号并分别送入两个ADPLL通道,读出两通道的PIR与PA并做差,差分结果可以将输入信号噪声抑制为公共项,从而只保留环路自身的噪声贡献。

该方法兼顾了可控性和重复性,便于长时连续采集以获得低频(mHz级)噪声谱。 在一系列位宽调整与参数微调的测试中,实测结果与理论模型高度一致。PIR位宽从40位降低到36位的测试显示低频处出现1/f型噪声台阶,完全符合PIR读出噪声理论的预测。PA读出在位宽较小时表现为白噪声上限,其幅度与位宽指数相关。幅度量化引发的相位噪声在位宽不足时会超过PA读出噪声,从而成为主导项;若将PA位宽设置为幅度量化位宽高出2位,则可以把幅度量化噪声抑制至不可察测的水平。参数化的低通滤波器设计(比如二阶IIR)能够有效抑制相位检测中的二次谐波分量,并在结合较高阻尼比时保证充足的相位裕度,进而把非线性噪声与周期性伪谱控制在极低水平。

在实际工程实现中,还需注意若干关键细节。ADC抖动(jitter)会把输入频率转换为相位噪声,传统上通过在模拟前端注入主导频率参考的pilot tone并在数字域校正来降低ADC抖动影响。环路延迟D应在设计早期被精确预算,包括ADC采样、乘法器、查表延迟以及寄存器流水线带来的时钟周期延迟。对高采样率系统(例如80 MHz)而言,常见的环路内部逻辑会带来数个时钟周期的延迟,从而在高带宽设计中显著消耗相位裕度。因此在进行KP与KI量化并实现为位移运算时,需把延迟引入的相移计入相位裕度评估中。 数据下采样与滤波链也是工程实现的难点。

为了降低存储与后处理需求,通常要在FPGA中把实时相位数据下采到较低的速率,级联积分-梳型滤波器(CIC)是常见的去混叠实现。但CIC滤波在满精度实现时会显著增加输出位宽,需要在下游截断或去量化,这又引入新的读出噪声。因此推荐在下采样链路上慎重设计位宽保留策略,并把PA/PIR的差分读出放在截断之前以避免丢失有效位数。同时,当多个ADPLL通道追踪相同频率信号时,在读出前做PA差分可以抵消公共的线性斜坡分量,直接得到相对相位信息,这对干涉测量非常有用。 基于综上分析,给出若干工程化建议以供参考。首先,在设计初期明确任务噪声预算与接收光功率,以此估算最优闭环带宽并据此设置阻尼比与PI参数。

其次,在位宽分配上优先保证PIR与PA读出位宽满足目标读出精度要求,推荐PIR≥38位、PA≥7位;幅度量化位宽不低于5位,若条件允许选择更高位宽以降低幅度相关相位噪声。再次,为抑制截断伪谱与窄带噪声,应在截断前加入适当的抖动并采用合适的IIR低通滤波器抑制二次谐波,同时在实现中留出相位裕度以对抗时延引入的相移。最后,采用差分PA读出与数字分配测量方法进行长期噪声评估,以验证低频(mHz级)噪声性能并确保线性工作区内无周期性跳相或cycle-slip风险。 面向未来,自动环路增益控制将是提升系统适应性的重要发展方向。由于实际信号幅度有较大动态范围,定点增益或固定位宽的环路在极端条件下可能出现饱和或精度退化。自适应增益控制结合在线噪声估计可以在不同信号环境下动态调整环路带宽,兼顾跳相鲁棒性与低噪声读出。

另外,多通道协同处理、硬件友好的滤波器结构优化以及对ADC抖动更高效的校正算法也将有助于把ADPLL应用推广到更广泛的高精度测量场景,如光纤分布式传感、惯性传感器和高精度导航系统。 总之,全数字锁相环以其强大的数字可控性和良好的抗干扰特性,为高精度相位测量提供了明确可行的技术路线。通过系统性的带宽与噪声平衡分析、合理的位宽筹划以及在FPGA平台上的充分验证,可以在满足皮米级位移与微弧度级相位精度的前提下,实现稳定、可扩展且资源高效的相位计设计,为空间引力波探测和其他高精度测量任务奠定可靠的读出基础。 。