Intel 386处理器于1985年发布,是首款引入32位架构的x86处理器,标志着微处理器设计迈入了一个新的阶段。在这款开创性的芯片中,寄存器电路作为核心组成部分,不仅承担着快速存储的重要角色,同时因其兼容早期16位及8位架构的需求,展现出极其复杂且优化的电路结构。通过对386处理器硅片的深入研究与分析,我们能够揭开其寄存器电路设计中的种种技术细节,理解Intel为实现性能与兼容性的平衡所作出的工程创新。作为处理器中极为关键的存储单元,寄存器拥有比主存更快的访问速度,直接影响处理器的整体运算效率。386寄存器组包含通用寄存器、索引寄存器、段选择器,以及专为内存管理和操作系统实现设计的特殊寄存器。其设计面临一大难题,即如何在保留对早期8086处理器的兼容性,支持8位和16位访问的同时,实现完整的32位存取和高性能并行读写操作。

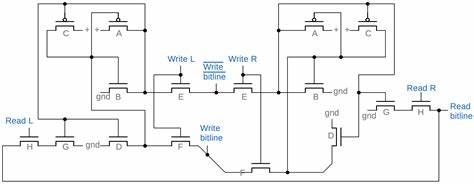

386的寄存器电路不仅体现在数量上,而是在实现方法上采用了六种不同的静态存储单元回路设计,不同类型的寄存器根据自身访问需求优化电路结构。他们中包含独特的6晶体管(6T)和8晶体管(8T)静态存储单元,每一晶体管扮演着关键角色以保障数据的稳定存储和访问。6T单元由两组反向输入的逆变器组成,可通过传输门控制位线进行读写操作。这种结构虽然紧凑,但由于数据读取与写入共用同一条线路,导致无法同时进行读取和写入。8T单元则通过添加两个额外晶体管,实现了读写端口的分离,使得处理器能够一边读取一个寄存器的内容,同时写入另一个寄存器的值,大幅提升寄存器文件的操作效率。在具体实现中,386处理器的寄存器阵列被设计成一张以行列形式排列的存储区域,行代表不同寄存器,列代表位数。

水平方向的字线(wordline)控制寄存器的选取,垂直方向的位线(bitline)传递数据位。这些硬件结构均为最大化性能、最小化芯片面积而精心设计,令整个数据路径逻辑布局如同“微型乐高积木”般整齐排列。386共有30个目标寄存器,其中22个是32位宽,8个是16位宽。Intel针对不同寄存器的读写需求,设计了6种不同的寄存器存储单元电路,从最简单的16位双端口8T单元,到复杂的10T单元以支持三端口访问。这种复杂的电路布局不仅满足了处理器在多端口同步访问上的需求,更解决了x86架构向后兼容带来的设计难题。例如,EAX、EBX、ECX和EDX这四个通用寄存器需要支持8、16、32位的多种访问方式,因而采用了拥有三条读写控制线的10T单元,支持部分字节的独立写入。

而像ESP、EBP等其他通用寄存器,则采用支持16位和32位写入的电路,减少设计复杂性。16位的段寄存器则用较为简洁的8T电路实现。在386芯片的物理布局中,寄存器阵列的宽度以每个位60微米为基础单位,保证各个单元能够像搭积木一样精确组合。然而其中16位寄存器采用了高密度的设计,在相同横向宽度中并排放置了两个寄存器位,实现了更高的存储密度。这种设计巧妙地提升了寄存器文件的存储容量,同时保持了芯片尺寸的紧凑性。对于支持8位访问的寄存器设计,Intel还面临数据定位与访问顺序的问题。

典型的x86架构允许将32位寄存器中的部分位(如低16位或低8位)访问为独立的16位或8位寄存器,如将EAX的低16位访问为AX,低8位访问为AL,中间8位访问为AH。为了处理这些不同宽度和段的访问,386的寄存器文件采用了一种独特的“洗牌网络”,将寄存器中低16位的两字节位线物理交错排列,使得对AH与AL寄存器的访问能通过电路中复用的多路复用器轻松实现位移而无需复杂的布线。这种交错方式既保证了高效的数据路径,也减少了电路线的复杂程度,体现了Intel在工程上的巧妙折衷。而在寄存器控制信号设计上,386更进一步采用了多个控制线路以支持分段写入功能,例如允许同时写入寄存器的低8位、高8位或高16位,实现对寄存器不同部分的独立操作。部分寄存器还能支持三端口访问,允许同时读取两个寄存器并将结果写入第三个寄存器,满足高效流水线执行需求。对于部分特殊寄存器,386甚至设计了可直接从相邻寄存器复制数据的功能线路,避免通过读写总线进行操作,提高了响应速度和系统吞吐量。

由于x86架构对历史版本兼容性的严苛要求,386的寄存器设计受限于必须兼容早期多代处理器的寻址方式和存储访问习惯,导致了这种非寻常的结构布局。Intel工程师以高度复杂的工艺,在有限面积内整合多个不同电路设计方案,使得寄存器文件能同时兼顾速度、密度、兼容性和功能丰富度,令人赞叹。在对386硅片的微观结构观察中,还能显现出寄存器与算术逻辑单元(ALU)之间通过垂直位线和水平控制线交叉配合的布线架构,功能单元条带式的排列,展现出高度规律性与模块化。所有这些细节共同支持了386处理器卓越的运算效率。总结来看,386处理器寄存器电路是兼顾性能和兼容性极致挑战的典范。6种不同的寄存器电路设计、三端口寄存器实现高并发读写、寄存器内位交错以及多段写控制信号,使得这款芯片在其诞生年代实现了跨时代的计算能力。

与此同时,这些复杂且高密度的电路设计也反映了x86架构为保证旧有软件生态持续运行,所带来的设计负担。相比之下,后续基于精简指令集计算(RISC)理念的处理器设计,避免了类似的复杂性,追求简洁和高效。Intel 386寄存器的设计历程不仅是一段技术史话,也为现代处理器设计提供了启示与借鉴。如今,在半导体工艺和架构设计飞速发展的背景下,细致研究这些早期高复杂度电路,能够帮助我们理解集成电路设计上的取舍权衡,乃至CPU架构演进的必然趋势。借由深入剖析386处理器寄存器的复杂电路,我们得以欣赏那些看似微小却承载重任的存储单元如何赋能计算机处理器的智能和高效。