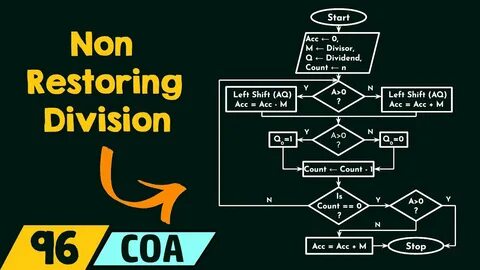

除法运算作为计算机科学及数字电子领域的重要组成部分,其高效实现一直备受关注。在众多除法算法中,非恢复除法算法以其独特的运算机制和性能优势成为研究热点。然而,许多学习者和工程师在理解和应用该算法时仍存在诸多困惑和疑问。本文将深入探讨非恢复除法算法的原理、实现步骤及常见疑难点,帮助读者系统掌握该算法的内在逻辑及实操技巧。首先,非恢复除法算法源自二进制除法的逐步逼近思想,旨在优化传统恢复除法中的重复加减操作。在传统恢复除法过程中,每次部分余数判断失败后,均需恢复之前的状态,从而增加不必要的计算负担。

而非恢复除法算法通过引入符号位的灵活处理,避免了频繁的恢复操作,有效提升了计算效率。具体来说,非恢复除法步骤包括初始化余数寄存器和商寄存器,然后依据被除数和除数的符号分别进行减法或加法操作。每一步操作都根据部分余数的符号决定下一步的加减方向,最终通过符号判断调整商的位值。算法强调部分余数符号与下一位商的确定息息相关,这种紧密联系是理解算法的关键所在。非恢复除法算法的核心优势在于减少运算周期,尤其适合硬件实现中的并行处理和流水线设计。其简化状态切换及减少反馈路径的特性,使数字信号处理器和微处理器能以更低延迟完成精确除法运算。

然而,在实际操作中,非恢复除法算法也面临若干难点。首先是符号处理的复杂性,不同操作步骤中符号的取值和转换容易导致误差。其次,部分余数寄存器的位宽设计和溢出处理成为设计的瓶颈,错误的位宽选择会引发溢出或数值失真。此外,最终商的符号修正和余数的正确性验证也需特别关注,以防止结果偏差。针对这些疑点,建议在算法设计时,采用符号扩展和溢出保护机制相结合的策略。在符号扩展方面,可通过高一位扩展来确保符号正确表达,避免减法与加法间的符号混淆。

同时,增加余数寄存器的安全范围,并设计合理的边界检测,有助于防止潜在的溢出错误。为了验证商和余数的准确性,算法结束后应增加结果校验步骤,如将商与除数乘积加余数,与被除数进行比对,确保无误差。这种严格的校验流程是保障算法稳定运行的基础。从应用角度来看,非恢复除法算法广泛应用于数字信号处理、计算机算术单元设计及嵌入式系统中。其硬件友好性使得设计者能够在资源受限环境中实现高效精度兼备的除法操作。不仅如此,算法的模块化设计便于与其他算术运算模块组合,形成完整的算术逻辑单元组合体。

为了进一步提升非恢复除法算法的实用价值,当前研究关注点包括算法的流水线优化、多位同时处理以及与其他算法的混合使用。流水线优化旨在减少单个除法操作的时钟周期,提高整体运算吞吐量。多位同时处理方法通过并行计算多个商位,显著加快除法速度,但对硬件布局和控制逻辑提出了更高要求。混合算法则结合非恢复除法的效率与其他如恢复除法或恢复余数算法的准确性特征,实现灵活的性能平衡。此外,软件层面上的优化也不可忽视。通过巧妙的代码实现和硬件指令集优化,可以最大化算法效率。

利用专门的除法指令或协处理器,还能进一步减少主处理器负担,提高运算速度和响应能力。研发人员需把握底层硬件特性,合理设计缓存和流水线,以达到算法性能与系统资源的最佳匹配。总结来看,非恢复除法算法作为一种高效二进制除法实现机制,凭借其独特的符号处理和状态更新策略,有效克服了传统恢复除法的弊端。全面理解其算法流程、符号机制及溢出处理,是解决实际应用疑难的关键。通过合理的硬件设计与软件优化,可以发挥该算法在现代计算领域中的巨大潜力。对于学习者和工程师而言,全面掌握非恢复除法算法不仅有助于深化数字电路和计算机组成原理的理解,也为提升实际系统设计能力奠定坚实基础。

未来随着计算需求的不断增长,非恢复除法算法仍将在高速、高精度数字运算中保持重要地位,值得持续关注和深入研究。 。