随着深度学习和高性能计算的快速发展,硬件加速器尤其是图形处理单元(GPU)在科学计算和人工智能领域中的地位日益重要。Nvidia推出的张量核心通过支持混合精度计算,提高了矩阵乘法的计算效率,极大推动了相关应用的发展。然而,尽管这些张量核心性能强大,其具体的计算行为和精度控制机制却未被广泛理解,也缺乏系统的描述。这给硬件模拟、工具开发以及算法设计带来了挑战。为了填补这些知识空白,研究者们采用了多种测试手段,但这些方法往往依赖人工设计,难以适应硬件的迭代更新。在此背景下,使用SMT(统计模型检测)技术对混合精度矩阵乘法过程进行形式化建模成为了关键突破。

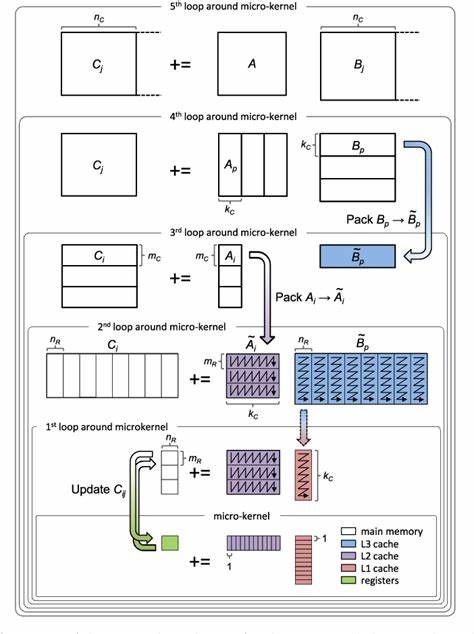

本文将围绕这项方法展开详细解析,重点探讨Nvidia三代张量核心——Volta、Turing和Ampere的行为机制及其差异。张量核心作为加速矩阵乘法的专用硬件单元,在执行浮点数乘法和累加时引入了多种非标准运算,包括不同的舍入模式、精度等级以及累加顺序等。这些因素直接影响计算结果的准确性和性能表现。以往研究多集中于实验测试和经验分析,缺少严密的数学模型支撑。而SMT技术采用逻辑约束的方式对硬件行为进行描述与验证,有助于全面揭示复杂的运算特性和潜在问题。通过构建详细的形式化模型,研究人员确定了影响张量核心运算的关键属性,分别包括舍入模式的选取、参与计算的浮点精度规格以及累加操作的执行顺序。

随后,利用自动化机器验证工具生成针对不同架构设计的区分性输入,能够准确捕捉各代机器之间在运算规则上的微小差异。例如,通过形式化模型的验证发现,之前文献中曾报告Nvidia在累加过程中采用了“向零舍入”策略的结论并不完全正确。实际上,这些设备并未实现该舍入方式,而是采用了更复杂的机制以保证累计结果的精度。此外,对于五项累计器中需使用额外进位位的需求也得到了确认,这对硬件设计提出了更高的准确性要求。基于这些严谨的发现,研究团队进而分析了当前广泛应用的两种基于半精度张量核心的单精度矩阵乘算法。这两种算法旨在利用硬件加速性能提升,同时通过算法级别的误差纠正降低计算误差。

经过形式化验证,令人意外的是,尽管后一版本的算法被设计为更为精确,但在特定输入条件下其误差表现却不如前者。这一结论对算法优化及硬件结合设计提出了新的挑战,促使开发者需重新审视训练和推理过程中数值误差的管理策略。从行业应用角度看,混合精度矩阵乘法在深度神经网络训练、科学模拟、图像处理等众多领域具有重要价值。形式化的SMT建模不仅为理解和验证硬件性能提供了有效手段,同时也为后续算法的鲁棒性和准确性分析奠定了基础。未来,随着计算架构进一步多样化与精度需求提升,这种基于形式化验证的研究路径将愈发关键。总之,借助SMT技术对三代Nvidia张量核心混合精度矩阵乘法的形式化描述,能够精确刻画硬件行为差异,发现传统测试难以揭示的细节问题,为硬件设计优化和算法开发提供科学参考。

此方法的推广应用将推动混合精度计算在更广泛领域的可靠部署,加速人工智能及高性能计算的技术革新。