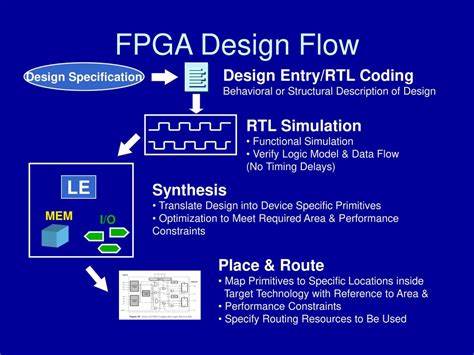

现场可编程门阵列(FPGA)在现代电子设计中发挥着越来越重要的作用,广泛应用于通信、图像处理、人工智能和工业控制等领域。随着需求的不断升级,FPGA开发也逐渐从传统的硬件描述语言设计走向软硬件协同的异构系统开发模式。结合软件、高级综合(HLS)、OpenCL以及寄存器传输级(RTL)设计,现代FPGA开发流程实现了前所未有的灵活性和高效性。本文全面介绍如何通过软件工具链、OpenCL编程模型和RTL设计实现FPGA的开发,确保设计者能够打造高性能且可扩展的加速系统。首先,理解FPGA开发流的基础架构是关键。以Zynq UltraScale+ MPSoC和Versal为代表的平台,采用Vitis统一软件平台和Vivado设计套件,支持在单一环境下完成硬件平台定义、内核开发、系统集成与应用部署。

Vitis异构系统设计流程独特之处在于能够集成嵌入式软件、高级综合模块、模型基础设计模块、AI Engine加速单元和传统RTL核,打造丰富多样的软硬件协同架构。开发者可通过Vivado创建可扩展的平台,定义时钟分频、复位逻辑、AXI接口布局及中断配置,导出硬件系统架构文件(XSA),随后导入Vitis完成平台的软硬件环境搭建,包括嵌入式Linux内核、根文件系统(RootFS)和构建工具链中的SysRoot。软件方面,借助Vitis平台创建工具将预先准备的Kernel Image、RootFS和SysRoot关联进项目,然后构建成可支持各种嵌入式应用开发的完整系统平台。为了验证开发流程及平台的有效性,Vitis自带的示例项目如简单双向向量加法为开发者提供实测环境,完成平台验证之后即可将镜像写入SD卡,直接加载运行于目标硬件。自定义应用的实现则体现了FPGA设计的强大能力。以系统监控器(SysMon)模块为例,该IP核通过采集外部模拟信号,为后续的信号处理算法提供实时数据输入。

通过在Vivado中添加SysMon以及自定义的RTL转换核(例如将SysMon输出转换为AXI-Stream接口信号),实现异构数据流在FPGA内部的灵活交互。RTL设计环节中,设计者需要精确编写接口约束以及数据传输逻辑,使得硬件信号能够无缝传递至后续的计算模块。与传统全硬件描述语言设计不同,现代FPGA项目大量引入HLS技术。以Vitis HLS为核心,开发者只需使用C++等高级语言描述算法,比如数字滤波器、FFT变换等,便可自动转换为高效硬件流水线。有针对性的接口定义(如AXI-Stream接口的声明以及控制接口的禁用)不仅确保模块资源利用最大化,还显著降低开发门槛。通过HLS设计的低通滤波器便是典型示例,该模块利用滑动窗口平均算法对模拟信号进行滤波,有助于滤除噪声并提高后续信号处理准确度。

在系统集成阶段,理清硬件内模块间AXI Stream流的连线关系至关重要。通过专门的连接配置文件指定模块间数据链路,如将SysMon Adapter输出连接至低通滤波器输入,进而连接到向量加法核的输入流,从而实现全数据路径的流水线传输,极大降低访问外部存储的频率,提高数据处理效率。软件层面,OpenCL作为高效异构计算编程接口,为FPGA加速器编程提供了统一的抽象接口。利用Xilinx提供的XRT运行时库,开发者能够方便地管理设备资源、分配缓冲区、传输数据并调度加速核。从主机程序调用角度看,开发者只需通过API加载xclbin二进制文件,映射缓冲区数据,设置核参数,发起任务调度,即可实现软硬件协同的高效计算。内核程序通过OpenCL描述运行机制,调度单元串行或并行工作。

代码示例显示如何通过映射和解除映射缓冲区完成数据交互,确保数据一致性。FPGA加速器的设计测试时长不容忽视,包含内核构建、系统合成、SD卡镜像生成等多个环节。整体耗时虽长,但多轮迭代开发及硬件仿真工具的支持有效提升开发者修正设计漏洞和性能瓶颈的效率。此种整合软硬件一体化开发流程,适用于多种FPGA开发板,不仅限于Avnet ZUBoard,还能拓展支持其他基于Zynq、Zynq MPSoC及Versal器件的嵌入式平台。同时,借助Vitis Vision Library等额外资源,可扩展至图像处理、视觉识别等复杂应用场景。整体来看,现代FPGA开发不再完全依赖传统寄存器传输级设计,而是依托Vitis和Vivado等高效统一工具链,打开了软硬件协同设计的新局面。

开发者能够从平台搭建入手,结合RTL、HLS和OpenCL多种设计范式,构建复杂数据处理流水线,提升开发速度与系统性能。以未来趋势而言,FPGA面向异构加速和智能边缘计算的角色将进一步强化。随着AI Engine图加速模块、动态可重构技术以及统一软硬件编译框架成熟,FPGA加速器开发的门槛会持续降低,普及度和应用深度同步提升。掌握软件、OpenCL及RTL多维度开发能力,将帮助嵌入式工程师和FPGA设计者开拓创新项目,推动智能硬件更快融入现实生活。