近年来,量子计算作为推动信息技术革命的核心动力,吸引了全球学术界和工业界的广泛关注。在实现高性能量子计算机的道路上,提高量子比特操作的保真度是当前的核心挑战之一。量子比特的保真度直接决定了量子算法的准确性和计算效率,因此,降低能量弛豫和去相干带来的信息丢失对于实现实用化至关重要。超导量子比特因其制备工艺成熟且易于集成,成为量子计算硬件的主要候选。本文围绕超导跨导型量子比特(Transmon qubit)操作保真度的提升,梳理最新实验数据及技术创新,提供深刻洞察。超导跨导量子比特作为实现量子处理器的基础元件,能够通过约瑟夫森结和电容网络实现量子态的制备与操控。

长期以来,这类量子比特面临的主要瓶颈是相对较短的能量弛豫时间(T1)和去相干时间(T2),引发了激烈的研究探讨以延长其寿命和稳定性。近期研究在设计与制造工艺上取得显著突破,推动了能量弛豫时间向毫秒尺度迈进。最新成果显示,采用优化的薄膜沉积与图案化技术,结合高纯度铌膜和精准的电子束光刻,成功制备出寿命远超以往的高相干性跨导量子比特。具体而言,研究人员通过调整约瑟夫森结的关键参数以及改进电磁环境屏蔽,有效抑制了各种环境噪声源对量子态的干扰,显著提升了操作的稳定性。量子比特的能量弛豫时间T1反映了量子态从激发态衰减至基态的时间尺度,是衡量量子元件损耗的关键指标。而回声去相干时间T2^echo则关乎量子态在噪声环境下的相干保持能力。

提升T1与T2^echo的关键在于材料质量、器件结构设计和环境隔离技术的优化。实验数据表明,通过使用高阻抗单晶硅基底以及高纯度电子束蒸发铝层,可以极大降低界面缺陷和杂质引发的能量损耗。此外,研究者还设计了具有集成普塞尔过滤器(Purcell filter)的共面波导谐振腔结构,减少量子比特能量通过读出线泄漏,有效延长了能量弛豫时间。值得注意的是,为了提升去相干时间,研究团队引入了三波混约瑟夫森行波参数放大器(TWPA),在低温环境中实现微波信号无失真放大,提高了量子态测量的信噪比,减少环境噪声对状态读出的影响。实验过程中严格控制样品暴露时间、表面氧化和材料处理流程,避免因表面质量下降导致的噪声增加和寿命缩短,为复合制程的量子芯片量产奠定基础。此外,采用低温磁屏蔽和辐射屏蔽技术降低环境电磁波干扰,提升量子比特场效应的稳定性。

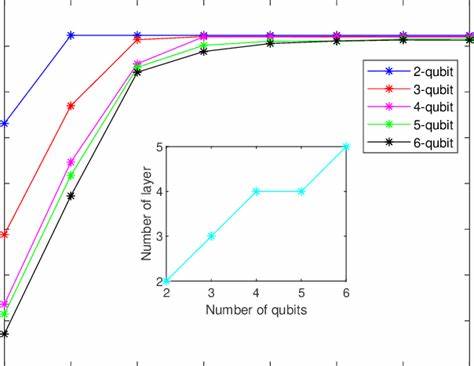

量子芯片制造方面,运用电子束光刻精确定义约瑟夫森结尺寸,实现关键电流密度的可控稳定,确保量子操作的重复性和一致性。同时结合等离子体刻蚀控制铌薄膜图案,避免材料机械应变引发的缺陷。工艺创新包括样品预先切割以减少暴露时间,以及多次真空纯化轮次保证蒸发室内杂质最小化,实现高质量的多层硅和铝结构叠加。测量平台融合了超低温稀释制冷系统、多级射频滤波及衰减器,以及基于Xilinx RFSoC硬件的精准数字信号生成与采集,实现了纳秒级脉冲控制和单量子测量。该系统支持在多轮冷却过程中的反复测量,确保结果的重复性和可靠性。通过长期动态观测,记录了能量弛豫和去相干时间的波动趋势,揭示了环境中的时变扰动因素如何影响量子比特寿命。

提升量子比特操作保真度不仅仅是提升器件本身性能的挑战,更涉及系统级设计。如在量子电路中引入纠错码,提高容错能力,能够在一定噪声环境下保持逻辑量子比特的稳定性。同时,硬件层面的进步为更大规模量子计算机铺平道路,使得多量子比特之间的高保真交换和纠缠操作成为可能。未来展望中,持续优化超导材料的表面和界面,进一步减少介电和磁性缺陷将是重点方向。应用机器学习等智能算法分析环境噪声,有望实现动态补偿和实时校正,极大增强系统鲁棒性。另外,量子芯片制造迈向工业化和大规模集成,将促使量子处理器性能与成本效益达到新的平衡点。

综上所述,基于最新的材料科学、纳米制造技术和量子测量手段,超导跨导量子比特的能量弛豫和去相干时间正大幅提升,推动保真度革命,距离千兆量子门操作乃至实用量子计算迈出坚实一步。随着设计不断迭代,制程日趋成熟,以及测量环境的精密控制,未来高保真量子比特不仅会带动先进的量子算法实现,也将加快量子信息科学和技术的产业化步伐,引领下一个信息时代的变革浪潮。