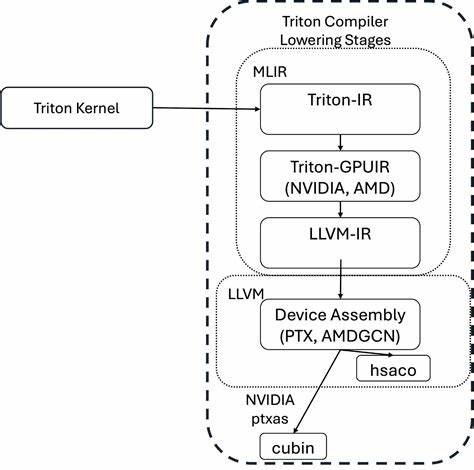

随着人工智能、大规模深度学习模型以及高性能计算需求的迅猛发展,分布式多GPU编程已成为推动行业技术进步的关键环节。然而,如何实现简洁、灵活同时高效的多GPU协同计算,一直是困扰开发者和研究人员的难题。在这一背景下,AMD研究与高级开发团队推出的Iris框架应运而生。作为基于Triton的多GPU编程解决方案,Iris通过远程内存访问(RMA)技术,实现了类似SHMEM的简单直观API,为多GPU编程赋予了全新的第一类公民地位。 Iris框架设计理念的核心是"让多GPU编程像单GPU编程一样简单"。开发者无需掌握复杂的分布式通信细节,只需要通过提供的RMA接口便能轻松实现跨GPU的数据读写操作,极大降低了多GPU编程的门槛。

基于Triton成熟的高性能编程模型,Iris不仅继承了其卓越的执行效率和灵活性,还支持细粒度的同步与通信重叠,加速了分布式计算任务的执行速度。 在具体实现上,Iris聚焦于提供SHMEM风格的远程内存访问,支持对称堆内存分配,确保不同GPU之间能够高效访问彼此的显存空间。此外,Iris公开了用户友好的Python接口,通过与PyTorch分布式通信框架的无缝集成,实现跨GPU进程的通信初始化和上下文管理。示例代码展示了在两个GPU之间利用Iris进行数据写入的流程,开发者可以通过简单的kernel定义与启动,实现数据在远端GPU显存上的写入与同步。 除了传统的API设计,Iris还推出了基于Triton Gluon的实验性后端。Gluon作为Triton的低层语言,允许开发者显式控制内存布局和数据移动,从而获得极致性能调优的能力。

该后端通过@gluon.jit装饰器提供了一种更加模块化和高效的编程模式,使得多GPU远程内存操作更加灵活且便于扩展。虽然目前仍处于实验阶段,但这一创新为未来GPU编程开辟了更多可能性。 Iris的安装和部署过程也充分考虑了开发者的便利性。支持通过pip直接安装最新版本,兼容主流的Python 3.10+和PyTorch 2.0+版本,同时依赖ROCm 6.3.1及以上的HIP运行时环境。针对开发环境,Iris官方推荐采用Docker Compose方案,可快速搭建具有代码热更新能力的开发容器,为代码调试和改进提供极大便利。对于裸机部署或其他容器方案,项目文档中也提供了详尽的指导,确保用户能够灵活选择最适合自身需求的运行环境。

目前Iris主要支持AMD旗下的MI300X、MI350X及MI355X GPU,对于其他ROCm兼容的设备也有一定的适配潜力。未来开发路线规划中,Iris团队计划扩展更多GPU型号的支持,增强远程直接内存访问(RDMA)以实现多节点分布式计算,进一步完善端到端示例和编程模式,从而覆盖更广泛的应用场景。 Iris作为一个开源项目,积极欢迎社区贡献。无论是在核心功能扩展、性能优化,还是在文档编写和示例完善方面,用户都能找到贡献入口。项目除了维护GitHub Issues平台供反馈,还提供直接联系开发团队的渠道,确保技术支持和交流的顺畅。这样的开放生态不仅加速了技术迭代,也促进了多GPU分布式计算技术的普及和发展。

从宏观角度看,Iris为分布式GPU编程树立了全新的标杆。它不仅显著降低了跨GPU通信和同步的复杂度,还借助Python的易用性和Triton的底层性能优势,实现了极具竞争力的性能表现。特别是在处理大型语言模型(LLM)、图神经网络(GNN)以及科学计算等场景时,Iris有望成为构建高效可扩展分布式训练和推理系统的重要工具。 未来,随着硬件架构的演进和异构计算需求的增长,Iris或将结合更多底层硬件加速技术,包括更低延迟的通信机制和动态资源管理策略。此外,跨节点的分布式计算支持也将使得Iris从单机多GPU延展到多服务器集群,满足更大规模的算力需求和任务复杂度。配合持续优化的开发工具链和更丰富的应用案例,Iris有潜力推动整个GPU计算生态迈向更加智能和高效的新阶段。

总结来看,Iris以其创新的RMA机制和基于Triton的多GPU编程架构,开创了多GPU程序设计的新范式。在保持简单易用的同时,兼顾性能和扩展性,极大地提升了分布式GPU编程的可达性和效率。随着社区日益壮大和技术不断完善,Iris将成为支持未来高性能分布式计算及机器学习的重要基石,值得GPU开发者、研究人员和企业技术团队高度关注和深入探索。 。