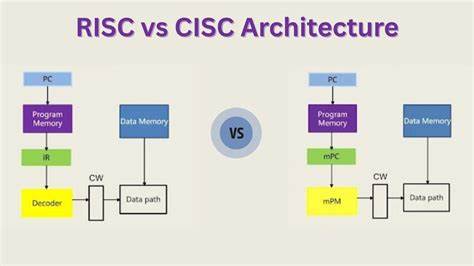

在计算机体系结构的讨论中,简化指令集计算(RISC)与复杂指令集计算(CISC)常被拿来比较,作为评估指令集设计理念与微架构实现之间关系的经典对照。很多讨论往往聚焦于指令集自身的复杂度或历史背景,而忽视了硬件组织对最终性能的关键影响。本文以"相似硬件组织"为前提,探讨当两种指令集运行在尽可能相同的硬件资源与组织下,它们的表现、瓶颈与设计权衡如何体现,以及对现代处理器设计的启示。通过理论分析与可重复的实验框架建议,读者可以更清晰地理解RISC与CISC之间的真实差异,以及如何在工程实践中做出选择。 从概念上讲,RISC强调指令简单、长度统一、寄存器为中心和易于流水线化,而CISC倾向于更复杂的指令、可变长度编码与内存操作更丰富的指令语义。历史原因使得两者在软件与硬件实现上各自形成了优化路径:RISC通过简洁的指令集减少每条指令的执行周期,CISC通过丰富的指令表达能力减少程序指令数。

若仅从静态指令计数衡量,CISC可能在代码密度上占优;但若将指令解码、微操作生成和流水线效率纳入评估,就需要更细致的比较。 设定"相似硬件组织"意味着在比较试验中为两种处理器提供尽量相同的基本资源:相同数量的通用寄存器、相同深度的流水线、相同的分支预测器和缓存层次、等价的时钟频率目标以及一致的内存子系统。关键在于将差异限定为指令集及其译码/微操作展开策略,从而观察指令集本身对性能和能耗的直接影响。此类控制变量的比较方法能够从体系结构学术研究迁移到工程决策中,避免将实现优化掩盖为指令集优势。 在这种设定下,性能衡量应超越单一指标。吞吐量、单线程延迟、每周期指令数(IPC)、每指令周期数(CPI)、功耗与能效(如每指令能耗或每操作能耗)都应纳入视野。

程序行为也必需多样化,既包括以整数运算为主的基准,也包括浮点密集型、内存访问密集和分支密集的负载。通过跨负载的综合评估才能揭示指令集与硬件组织之间的相互作用。例如在内存密集型程序中,指令集对代码密度的影响会直接反映到缓存命中率,从而影响整体性能;而在计算密集型负载下,指令的平均执行复杂度和流水线利用率则更为关键。 在相同硬件组织下,RISC的优势通常体现在更简单的解码路径和更高的流水线利用率。由于RISC指令多为固定长度且语义简洁,译码器和发射逻辑可以更直接地将指令映射为执行单元操作,减少译码延迟并简化流水线控制。这在高频率、深流水线的实现中尤为重要,因为每一级都要求低延迟和稳定的时序裕量。

另一方面,CISC在指令级语义丰富的情况下,往往需要更复杂的译码逻辑或微指令ROM来分解复杂指令,这会增加硬件复杂度并可能引入额外的微操作(micro-ops)序列,从而影响发射和调度阶段的效率。 然而,CISC并非注定在相似硬件组织下处于劣势。现代x86处理器已经证明,通过将复杂指令在前端译码为微操作,结合强大的动态调度与执行引擎,CISC也能达到高IPC和良好的频率表现。当硬件团队为两者配备等量资源时,CISC可以利用其指令表达能力减少程序的动态指令数,从而在某些负载中减少指令缓存和分支预测的开销,提升性能和代码密度带来的能效优势。关键在于微架构前端如何高效处理复杂指令并将其转化为与RISC等价的执行流。 能效方面,RISC的简单指令解码和较短的指令路径通常意味着更低的静态和动态功耗开销,尤其在嵌入式和移动终端中表现显著。

更少的译码和控制逻辑意味着在相同的工艺节点上可以节省布局面积和能耗预算,使得RISC在低功耗设计空间占优。但如果CISC的较高代码密度显著降低了指令缓存未命中率或缩短了内存访问周期,整体系统能耗可能受益于更少的内存访问,从而缩小甚至反转能效差距。因此,能效并不是单纯由指令集特性决定,而是指令集、编译器质量、缓存组织与应用工作负载共同决定的系统级指标。 编译器在相似硬件组织的比较中扮演着核心角色。高质量的编译器可以将高级语言构造映射为目标指令集的最佳序列,极大影响动态指令数和寄存器使用效率。在RISC平台上,编译器通常会生成更多的寄存器到寄存器操作,依赖寄存器分配策略来避免内存访问;在CISC平台上,编译器可能利用复杂指令将常见的操作序列合并为单条指令,从而降低代码体积。

为了公平比较,实验需要使用针对各自指令集调优过的编译器,并尽量在相等优化级别的前提下测量生成代码的性能和大小。 可重复的实验框架应包括一致的基准套件、相同的运行时环境和严格定义的测量方法。基准应覆盖整型计算、浮点计算、内存访问模式和分支预测敏感性场景,既有合成基准也有真实应用负载。测量应记录IPC、CPI、时钟频率、平均指令长度、L1/L2缓存命中率和功耗等关键指标。为排除实现偏差的影响,建议在微架构仿真器中实现两个指令集的处理模型,保证相同的流水线长度、相同的寄存器文件端口数和相等的执行资源。通过统计级仿真和周期精确仿真结合,可以得到既具有可比性的宏观结果,也能分析微观原因。

从实际工程角度出发,选择RISC或CISC常常不是单一性能指标能决定的。若目标是追求极限频率、简洁实现和低功耗,那么RISC往往提供更清晰的路径。嵌入式和移动设备中的许多成功案例证明了这一点。若目标是兼容大量既有软件、追求高代码密度或利用复杂指令简化编译器生成的代码序列,那么CISC可能更具优势。企业级服务器和桌面处理器的演进展示了通过复杂前端与强大后端结合,CISC也能在高性能领域占据主导地位。 现代趋势正在淡化传统RISC/CISC的分界。

许多处理器采用了混合策略:在指令前端做复杂指令的分解,将其转化为简洁的微操作集合,后端执行类似RISC的微架构策略。向量化、专用加速单元和异构系统的引入,使得单一指令集特征对整体性能的影响被更多层次的设计决策所稀释。对设计者来说,更重要的是明确目标工作负载、功耗预算与生态兼容性要求,然后在指令集简洁性与复杂性之间寻找适配方案。 结论上,在相同硬件组织条件下,RISC与CISC各有强弱:RISC倾向于更低的解码开销、更高的流水线效率和更易优化的硬件实现,而CISC通过减少动态指令数和提高代码密度在特定工作负载中提供优势。两者最终的胜负往往由编译器质量、缓存层次行为、分支预测效果以及前端到后端的微架构设计共同决定。对于工程实践而言,推荐采用可验证的比较方法在目标平台上进行评估,并在设计初期就将软硬协同优化纳入考量。

通过统一硬件组织下的对比实验,可以为架构选择提供基于数据的判断,而不是基于标签的讨论。未来的处理器设计将继续融合两种范式的优点,关注系统级优化与能效,而不是单纯依赖指令集理论的对立。 。