随着人工智能技术的迅猛发展,大语言模型(LLMs)已成为推动智能体应用进步的关键力量。特别是在涉及复杂指令、多轮交互以及长时间记忆的场景中,长上下文的智能体大语言模型推理需求日益增长。这类推理任务不仅优于传统的聊天机器人应用,更面临着更大规模的上下文信息处理挑战。如何有效突破记忆墙的限制,提升推理效率,成为当前研究与工程实现的重中之重。 长上下文智能体推理的核心挑战在于海量数据存储和高速访问需求。不同于简单的对话式模型,智能体推理需处理包括网页DOM结构、复杂工具调用轨迹等长序列输入,这使得大规模上下文状态管理必不可少。

频繁的长距离内存访问引发了严重的带宽瓶颈和容量限制,这被学界和业界称为"带宽记忆墙"和"容量记忆墙"。这两大瓶颈极大限制了芯片内计算单元的利用率,导致硬件性能难以充分释放。 面对上述挑战,一套高效的硬件软件协同优化方案尤为关键。近期的研究突破之一是PLENA系统,这是一种结合硬件设计与软件支持的综合平台,专注于优化长上下文智能体大语言模型的推理过程。PLENA的设计理念在于通过多方协同创新解决记忆墙问题,实现推理性能的飞跃。 PLENA采用了一种非对称量化机制,使硬件在数值精度和计算资源之间达到最佳平衡。

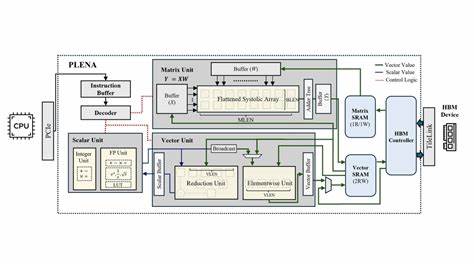

通过这一量化策略,可以显著降低内存占用和数据传输负担,同时维护推理的准确性和稳定性。硬件部分则采用了扁平化的流水线阵列结构,此架构针对长上下文推理任务特有的访问模式进行了优化,天然支持FlashAttention技术,有效缩减了计算过程中的内存访问延迟。 在软件层面,PLENA配备了专属的指令集架构(ISA)、编译器工具链及仿真模拟环境,形成完整的开发生态系统。这让研究人员和工程师能够通过自动化设计空间探索,对硬件和软件参数进行联合优化,以适应不同应用需求。模拟实验表明,相比现有加速器,PLENA能实现高达8.5倍的计算单元利用率提升,推理吞吐量分别超越主流GPU(如A100)和TPU v6e数倍,极大推动智能体模型的实际应用价值。 硬件设计方面,解决长上下文带来的内存带宽压力是首要任务。

PLENA通过流水线阵列内部高效调度,减少冗余数据移动,采用异步内存管理机制,最大限度降低外部内存访问次数。层层优化的设计不仅提升了数据重用率,还在芯片面积和功耗之间取得理想平衡,使得在边缘设备或高性能计算中心都具备良好的适用性。 软件策略则聚焦于推理流程的智能编排。针对大上下文推理中频繁出现的重复计算和状态检索问题,PLENA引入多级缓存机制和动态矩阵切分技术,加速注意力机制的计算。FlashAttention作为一种加速全注意力计算的尖端技术,被深度集成于平台架构中,显著缩短了长文本序列的推理延迟,提升模型实时响应能力。 此外,PLENA的自动设计空间探索系统借助仿真平台,结合机器学习算法,快速定位硬件-软件最佳配置。

用户能够灵活调整量化参数、阵列规模、缓存策略等关键变量,实现从研究验证到实际部署的无缝过渡。此模块有效降低了开发门槛,加速了创新成果的产业化落地。 从应用角度看,长上下文智能体模型在自动化工具操作、网页信息抽取、复杂命令行执行等领域展现出极大潜力。PLENA则为这些需求提供了坚实的算力保障,允许模型在处理海量且多样数据时保持高效稳定运行。未来,随着模型规模不断扩大和场景愈加复杂,类似PLENA这样融合硬件与软件深度协同的解决方案,将成为推动AI智能体技术持续进步的重要支柱。 综上所述,优化长上下文智能体大语言模型推理的路径,必然依赖于从芯片设计、计算架构到编译器工具链的多层协同创新。

PLENA系统通过其非对称量化、扁平化流水线阵列和FlashAttention等技术创新,成功突破了带宽和容量两大记忆墙,实现了显著的性能提升和资源利用优化。随着开源的推进,更多研究者和开发者将能够借助这套系统加速相关应用的发展,推动人工智能进入更深层次的智能交互和复杂任务处理时代。未来的研究方向还将涉及进一步降低能耗、提升适应性和扩展更多智能任务支持,为打造更强大的长上下文智能体体系奠定坚实基础。 。