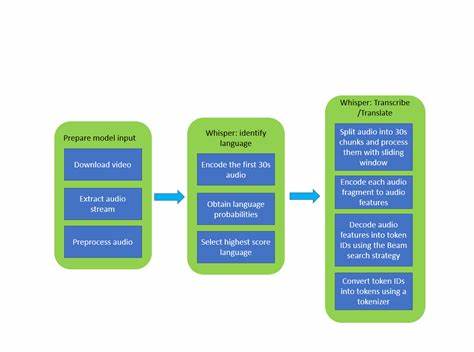

在现代数字电路设计中,三角函数的计算需求日益增长,尤其在信号处理、通信和嵌入式系统领域。传统的软件实现方法往往性能受限,无法满足高速和实时计算的要求。系统Verilog作为一种硬件描述语言,提供了高效表达硬件逻辑的能力,使得硬件加速三角函数成为可能。基于CORDIC算法的硬件实现可以显著提升计算速度和资源利用率,是数字设计工程师关注的重点方向之一。 CORDIC (Coordinate Rotation Digital Computer)算法是一种迭代式的数值计算方法,能够在不依赖乘法器的情况下,使用简单的移位和加减运算完成三角函数、反三角函数、对数和指数等复杂的数学函数计算。这使其非常适合硬件实现,尤其是在资源受限的FPGA和ASIC设计中。

系统Verilog代码中采用CORDIC算法,可以生成高度并行和流水线结构,实现高吞吐量和低延迟计算。 项目中通常包括正弦、余弦和反正切函数(atan2)的硬件实现,支持可自定义的输入输出位宽,满足不同精度需求。此外,设计分为流水线(pipelined)版本和非流水线版本,分别适合高吞吐量和低资源消耗的应用场景。流水线版本通过分阶段的计算避免了运算瓶颈,适合高速连续信号处理。非流水线版本则节省硬件资源,适合对功耗和面积敏感的场合。 系统Verilog模块的生成通常借助Python脚本进行自动化,用户可以指定输出文件路径、模块位宽及流水线开关。

自动生成的代码结构清晰,易于维护和集成。预生成的32位模块方便快速验证和移植,并配备了多种测试平台,包括模型仿真和波形分析文件,保证设计的正确性和稳定性。 尽管该硬件加速三角函数模块已经经过充分仿真测试,但在实际硬件上的验证仍是一个重要步骤。例如在基于Altera DE1-SoC等开发板上的综合和时序分析,将帮助工程师全面评估该设计在真实环境中的性能和功耗特性。未来版本还计划支持更多迭代次数的自定义,拓展超越当前位宽的计算精度,并加入除法和双曲函数等功能,进一步丰富模块的应用范围。 系统Verilog中基于CORDIC算法的三角函数硬件加速设计,不仅提升了数字系统的数学运算能力,还降低了对昂贵乘法器资源的依赖,优化了功耗与面积的平衡,在通信调制解调、雷达信号处理、数字成像等领域具有极大应用潜力。

对于FPGA和ASIC设计工程师而言,掌握此类高效数学模块设计方法,将为复杂算法加速和硬件定制奠定坚实基础。 总结来看,硬件加速三角函数的实现借助CORDIC算法的迭代特性,结合系统Verilog的强大描述能力,实现了精准且高效的数学运算解决方案。自动化脚本的辅助生成和全面的测试环境支持,降低了设计门槛,提升了工程效率。未来随着功能的不断完善和硬件验证的深入,基于此设计的三角函数模块将在各类高性能数字系统中扮演关键角色,推动行业技术向更高水平发展。 。