在计算机体系结构的设计中,操作码(opcode)的解码是指令执行过程中的关键环节之一。随着处理器功能的不断复杂化,操作码的设计和解码也变得愈发复杂。尤其是在微程序控制器中,微操作的多样性和并行性使得单一操作码表示所有控制信号的设计面临极大挑战。为了有效减小操作码解码器的复杂性,控制字段划分(control field division)技术应运而生。本文将全面解析控制字段划分如何帮助降低操作码解码器的复杂度,并深入探讨其背后的原理及实际应用价值。 操作码解码器的复杂性来源于其需要识别和翻译极其庞大的状态控制信号集合。

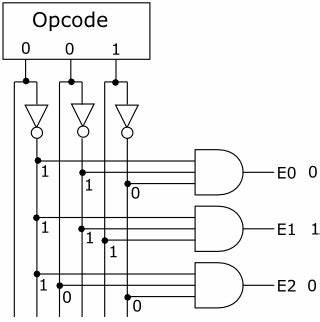

传统上,每一种可能的指令组合都需要有一个独立的操作码来描述其微操作序列。当微操作可以并行执行时,操作码的数量呈指数级增长,因为每个操作码必须覆盖所有可能的微操作组合。这不仅导致操作码数量爆炸,还使得操作码解码器的电路规模巨大,设计难度大,功耗和延迟也随之增加。 为解决这一问题,控制字段划分技术将复杂的微操作控制信号拆分成多个互不重叠的控制字段。每个字段专门控制一部分微操作,例如加法器、寄存器、总线等单个设备的控制信号。这样,每个控制字段负责有限的微操作集,相互之间可以同时执行,但解码过程被拆解成多个较小的解码单元,极大地降低了每个单元的硬件复杂度和逻辑深度。

这种划分带来的核心优势是降低了操作码组合的数量。原本如果将所有可能的微操作组合编码为单一操作码,其数量会随着并行微操作的增加呈指数增长。而通过控制字段划分,整体操作码被分割成多个较短的子字段,每个字段的状态数量远少于整个组合的总数。系统通过并行分析各个子字段的值,以判定各个控制信号的激活情况。这种方法有效避免了笛卡尔积式的操作码爆炸,从根本上降低了解码复杂度。 此外,控制字段划分还有助于微程序设计的模块化和灵活性。

设计者可以针对每个控制字段定义标准化的编码格式,集中优化各个子电路的性能和功耗。微程序调试和维护也因此变得更加简洁,因为每个控制字段只关心对应设备的操作,调试范围缩小,定位问题更加高效。 John P. Hayes在其著作《计算机组织与体系结构》中指出微程序设计层面支持多条微操作并行执行的本质,使得操作码必须能够准确表示这些并行组合。采用单一操作码全面编码所有组合,不仅需求量庞大,且解码器实现难度极高。通过将微操作规格分割为多个独立的控制字段,各字段独立控制不同设备的微操作,能够高效表达并行性,同时硬件解码负担减轻,从而提升系统整体的可实现性和扩展性。 在实践中,控制字段划分不仅适用于微程序控制器,在复杂指令集处理器(CISC)和精简指令集处理器(RISC)设计中也被广泛借鉴。

通过硬件模块化实现不同功能部分的控制信号独立生成,进而简化指令解码流程。更具规模的现代处理器甚至将控制字段细化到信号线级别,使得各部分控制逻辑高度并行且相互独立,显著提升指令流水线效率和多指令并发执行能力。 总结起来,控制字段划分技术通过分解控制信号,避免了操作码编码上的指数级膨胀,为操作码解码器提供了极大优化空间。它让复杂的微操作并行组合可以被拆分为多个更简单、硬件实现成本低的解码单元。控制字段的独立性和专用性不仅简化了电路设计,降低了功耗,还提升了系统的稳定性和可扩展性。随着芯片设计复杂度的持续增加,该技术仍将作为微架构设计中的重要手段,促进高性能计算机系统的实现与发展。

。