在半导体技术迅猛发展的今天,纳米级晶体管的设计与优化显得尤为重要。近年来,随着摩尔定律的不断推进,制造更小、更高效的晶体管成为了电子工程师和研究人员的主要任务。其中,纳米尺度的门全环(GAA)场效应晶体管(FET)因其优越的电学性能和优良的可扩展性,受到了广泛关注。然而,在GAA FET的设计过程中,如何有效地评估和微调其在不同应力条件下的表现,依然是一个亟待解决的技术难题。 最近,汉阳大学和Alsemy公司的一项新研究为解决这一问题提供了创新的思路。他们联合发布了一篇名为“基于神经网络的次3纳米门全环CMOS逻辑电路性能的应变影响”的技术论文。

研究者们通过建立基于神经网络的紧凑模型,评估了GAA FET在应变状态下的电路性能。这一研究不仅在学术界引起了广泛关注,也为未来的半导体器件设计提供了新的方向。 应变对半导体器件性能的影响已被广泛研究。在GAA FET的设计中,通过引入应力,可以优化器件的载流子迁移率,从而提高开关速度和降低功耗。然而,如何量化这种影响并在电路层面进行评估却并非易事。传统的模拟方法往往耗时较长,难以满足现代快速发展的产业需求。

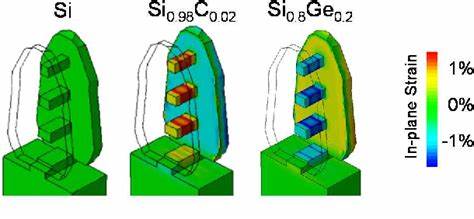

此次研究中,研究团队首先利用三维技术计算机辅助设计(TCAD)设备仿真数据,构建出包括nMOS和pMOS在内的GAA FET的行为模型。通过仿真技术,他们引入了材料之间的晶格失配,借此在GAA FET的通道中施加了拉伸和压缩应力。此过程使用了复杂的三维TCAD工艺模拟,以确保模型的精确性。 在此基础上,研究小组进一步对所建立的神经紧凑模型进行了校准,以提高其预测能力。针对高级蒙特卡洛仿真结果进行比对,这一过程确保了模型能够在多种操作条件下有效地反映GAA FET的真实表现。最终,该神经紧凑模型的预测误差低至1%,显示出其在准确度上的优越性。

为了研究应变对电路级性能的实际影响,研究人员采用SPICE模拟对五级环形振荡器和双输入与非门(NAND 门)进行了测试。结果显示,使用应变GAA FET后,五级环形振荡器的传播延迟从3.60皮秒下降到了2.85皮秒。这一显著的改进为高频电路的设计提供了新的可能性。此外,双输入NAND门的功耗与延迟积也得到了增强,提升幅度达到13.8%至15.5%,具体取决于输入电压序列的变化。 这项研究的成功不仅为GAA FET的设计提供了强有力的数据支持,也展示了神经网络在半导体建模中的应用潜力。通过神经网络模型,研究人员能够更快、更高效地评估不同制造条件下晶体管的性能,这在未来的集成电路设计中尤为重要。

尤其是在不断追求速度和性能的市场环境中,能够迅速迭代和优化产品成为了企业竞争力的重要组成部分。 此外,随着机器学习和人工智能技术的不断发展,基于神经网络的模型将有望在不断复杂化的半导体设计中扮演越来越重要的角色。这种新兴技术不仅能够提高建模效率,还能为设计团队提供优化建议,从而加速新型半导体器件的研发。 值得注意的是,虽然这项研究初步显示了应变在提高电路性能方面的巨大潜力,但仍需进一步的实验证实其在实际应用中的有效性。这包括但不限于在更为复杂的电路中测试这一模型的适用性,以及在不同材料和制造工艺下的表现。同时,研究人员也提到,未来将探索更多种类的应变及其对不同器件的影响,这一方向无疑将推动新一代半导体技术的发展。

总的来说,这项研究的成果为GAA FET及其在高性能电路中的应用奠定了基础。随着技术的不断进步,相关研究有望为可穿戴设备、物联网设备、智能手机等领域提供更高效、更节能的解决方案。在这一过程中,不断创新的科学研究和技术应用将是推动半导体行业前行的重要动力。 汉阳大学和Alsemy公司的这一跨界合作,不仅展现了学术界与产业界的紧密联系,也为未来半导体领域的持续创新提供了新的机遇。相信在不久的将来,基于这一研究成果的新型半导体器件将以更高的性能和更低的功耗,向我们走来。