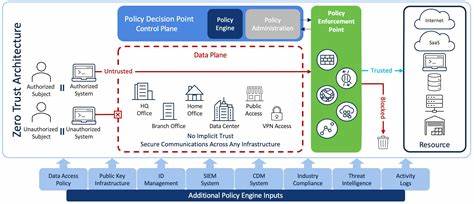

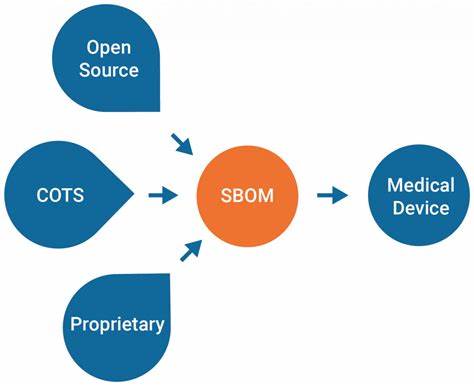

随着现代高性能处理器设计的发展,分支预测技术在提高CPU整体性能方面扮演着至关重要的角色。近年来,指令级并行度和流水线深度的不断提升使得分支预测的准确率成为限制处理器性能的重要瓶颈。为此,研究人员不断探索更智能、更高效的预测方法,RUNLTS(Register-Value-Aware Predictor Utilizing Nested Large Tables)便是一种融合寄存器值相关性与嵌套大表存储结构的创新型分支预测器,代表着分支预测技术的新的里程碑。RUNLTS基于业界公认表现出色的TAGE-SC-L预测框架,融入了对寄存器值与分支方向之间相关性的深度挖掘,结合优化的历史长度集与条目分配策略,成功实现了更高水平的预测准确率和硬件资源利用率。传统的分支预测器大多依赖历史路径信息和分支指令本身的统计特征,但往往忽视了寄存器值这一隐藏的丰富信息。寄存器中的值直接反映了程序运行时的即时状态,它能揭示出分支条件的内在逻辑。

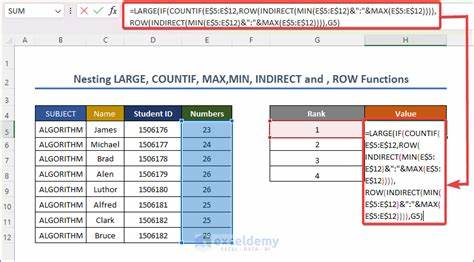

RUNLTS通过生成针对每个寄存器值的短摘要(digest),并将其与分支方向的相关性进行建模,捕获了寄存器状态对分支结果影响的微妙联系。此举显著提升了分支预测的精准度,特别是在复杂控制流和循环结构中表现尤为突出。RUNLTS采用了多层嵌套的大型预测表结构,这种嵌套表兼顾了存储容量与访问速度的平衡,通过智能分配和历史长度的重新设计,扩充了模型对长历史依赖的响应能力。具体来说,RUNLTS引入了一种全新的历史长度集合,突破了传统几何历史长度设计的限制,使得预测器可以更灵活、细粒度地捕捉分支行为的时间相关性。同时,它实现了对分支条目分配的高效控制,避免了预测表的资源浪费与冲突,保证了硬件资源被最大化合理利用。CPU流水线深度的加大在带来了性能提升的同时,也使分支预测错误的惩罚更加严重。

现代处理器如具备超过500条指令的重排序缓冲区,每次错误预测都可能导致上百条指令被清空,显著影响执行效率。RUNLTS针对这一挑战,整合了改进的内循环预测机制(IMLI),通过赋予内循环预测更高权重,提升了循环体分支的预测质量。这种设计特别适合现代应用中频繁出现的紧密循环和条件分支结构,进一步减少了错误预测带来的性能损失。此外,RUNLTS还借鉴并改进了调用栈历史机制以及流水线感知的预测更新方法,保证了预测状态的及时同步和准确更新,从而增强整体预测的稳定性和适应性。在大量实验和评测中,RUNLTS使用CBP 2025竞赛提供的训练跟踪数据,取得了令人瞩目的性能成果。其BRMisPKI(每千条指令的分支错误次数)和CycWpPKI(每千条指令的周期浪费)均显著优于现有领先预测器,展示了RUNLTS在应用于未来超大规模、高复杂度CPU设计中的巨大潜力。

展望未来,RUNLTS的研究思路为分支预测领域开辟了新的方向。寄存器值深度感知与嵌套大表架构的结合,不仅提升了预测的准确性,也为硬件设计提供了更多维度的优化可能。同时,RUNLTS的设计理念也适用于神经网络辅助预测和机器学习集成预测等先进技术,为智能计算时代的高效处理器架构发展提供坚实基础和启示。综上所述,RUNLTS作为一款先进的基于寄存器值感知的分支预测器,通过独特的嵌套大表结构和创新的历史长度策略,实现了在复杂现代处理器环境中的高效预测。它代表了分支预测技术演进的一个重要节点,不仅提升了单核处理性能,也为多核多线程环境下的调度与资源管理带来积极影响。随着计算需求的日趋复杂,聚焦寄存器值关联信息,结合大容量智能表结构的预测方法,将成为推动下一代高性能处理器设计不可或缺的技术利器。

。