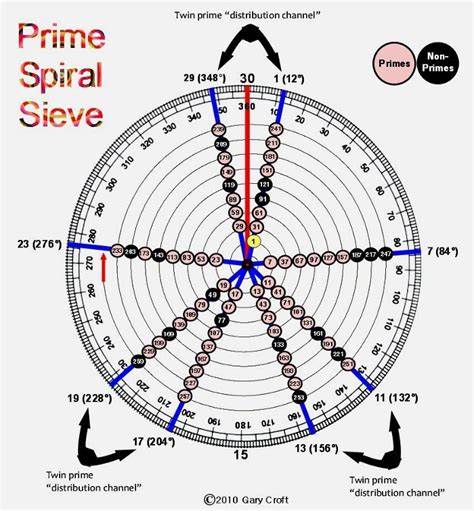

素数作为数学中基础且重要的数列,一直以来都是数论研究的焦点。随着计算技术的不断进步,能够高效地判断和生成素数序列对许多领域都具有重要意义。数值较大的素数在密码学、计算机科学尤其是加密算法中发挥着关键作用,因此研究素数筛算法的运行时间不仅具有理论价值,也具备显著的实际应用意义。 素数筛算法,顾名思义,是通过筛选的方法从自然数集合中筛选出所有的素数。最经典的素数筛算法莫过于埃拉托斯特尼筛法(Sieve of Eratosthenes)。该算法诞生于公元前三世纪,由古希腊数学家埃拉托斯特尼首创。

其思想非常简单:从2开始,将所有2的倍数筛去,再对下一个未被筛去的数的倍数进行筛选,直到达到目标数的平方根为止。工作原理虽然直观,但效率却高于逐一判断每个数是否为素数,尤其在中小范围内表现良好。 然而,埃拉托斯特尼筛法并非在大规模数据上表现最优。其时间复杂度大致为O(n log log n),虽然优于朴素算法的O(n√n)的复杂度,但随着n的增大,执行时间仍然显著上升。尤其对于需要筛选数以亿计甚至更大的范围时,标准的埃拉托斯特尼筛算法的空间消耗和时间消耗已成为瓶颈。为此,计算机科学家和数学家们陆续提出了多种优化和改良方法。

其中,线性筛算法(Linear Sieve)作为埃拉托斯特尼筛法的高效变种,通过保证每个合数仅被划去一次,理论上的时间复杂度达到了O(n)。线性筛的核心在于维护一个素数表和最小质因数数组,避免重复筛选,从而节省大量计算时间。实际应用中,线性筛算法在处理海量数据时表现出了极大的优势,广泛应用于需要快速素数生成的场合。 除了算法自身的优化,程序实现层面的改进也在运行时间上产生了显著影响。例如,位数组(bitset)的使用有效减少了内存占用,提高了缓存命中率,从而加速计算过程。此外,多线程并行计算的应用,将筛选过程分段并行执行,极大降低了运行时间,在多核心计算机环境下尤为明显。

并行埃拉托斯特尼筛和并行线性筛等方案被业界广泛研究和使用,大幅提升了算法在大数据背景下的实用性。 除了时间性能和空间消耗,算法的硬件适配性也是优化的关键。利用现代CPU的SIMD指令集能够实现单指令多数据的并行处理,加速素数筛的遍历与筛选过程。此外,GPU加速成为异构计算趋势下的研究热点,通过庞大的并行计算能力处理筛选任务,进一步缩短处理时间。近年来,FPGA硬件加速同样被尝试用于素数筛,结合硬件级别的定制电路实现,能够在特定应用中达到极致的性能表现。 素数筛算法不仅限于简单的筛选素数,扩展到其他数学问题中也发挥着作用。

比如,在求解某些数论函数、分解质因数甚至于密码学中的安全性分析,都或多或少依赖于高效素数筛的支持。因此,深入理解素数筛的运行时间和优化路径,对推动相关领域的发展具有积极影响。 如今,随着数据处理需求的不断增长,优化素数筛的运行时间既是算法理论上的挑战,也是计算实践的必然要求。尽管埃拉托斯特尼筛和线性筛提供了坚实基础,结合现代计算机架构的并行计算及硬件加速势必成为未来发展的重点。同时,算法设计上的创新也为解决大规模素数筛问题提供了可能。 未来,素数筛算法的研究仍将围绕提升算法效率、节约空间资源和兼顾硬件特性展开。

人工智能辅助的算法自动调优、异构计算与分布式计算的结合,都有可能突破现有的性能瓶颈,实现真正意义上的大规模快速素数筛。这些技术动向将加速素数理论研究和相关应用领域的技术进步,推动数字信息时代下的安全与计算能力发展。 综上所述,素数筛算法的运行时间不仅是衡量算法优劣的重要指标,也是优化工作的核心方向。从埃拉托斯特尼筛到线性筛,从单线程实现到多核并行和硬件加速,素数筛算法不断迭代演进,满足不断增长的计算需求。深入理解其运行时间特性和优化手段,能够帮助研究人员和开发者在实际应用中选择合适的算法方案,提高整体系统的性能和效率,为相关领域带来更多技术突破和应用价值。 。